Magnetic Bubble Memory (MBM) was positioned as a major contender for computer storage in the late 1970s, even appearing in popular culture when at the center of the plot in Knight of the Phoenix. The technology seemed to offer everything flash offers today, and is the basis of some surprising patents such as this iPod forerunner filed in 1979.

The TMS 9916 Bubble Memory Controller datasheet surmised,

…the main advantages are the low entry price versus disks…, nonvolatility…, and high-density storage… ideally suited for portable applications as well as providing memory for traditional processing systems

What Is Bubble Memory?

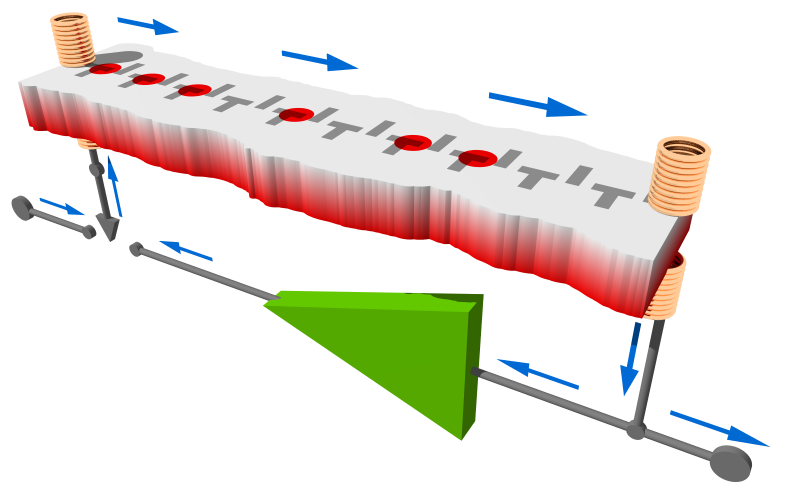

MBM works by storing bits as cylindrical magnetic domains (the bubbles) on a film mounted within an electromagnet array, which is used to move the bubbles through the film. Functionally, MBM is like a massive shift register – moving the bubbles results in one (stored) bit being read from one end, and a new bit being supplied at the other.

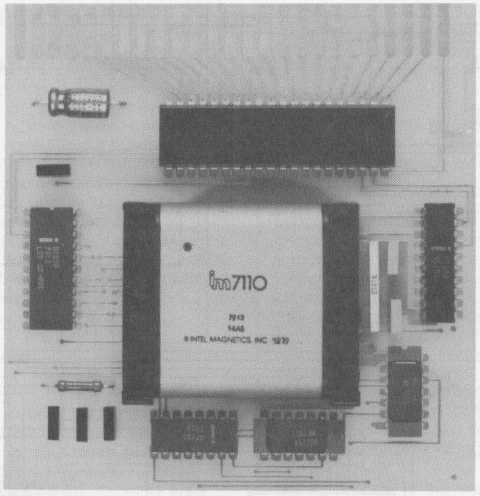

By the end of the 1970s, practically every major semiconductor manufacturer was working furiously on this technology, and of course Intel was no exception with its subsidiary ‘Intel Magnetics’. Their 1979 Design Handbook for the Intel Magnetics One Megabit Bubble Memory is well worth a look, and includes a technical article as an appendix with some performance specifications. The power consumption jumps out as surprisingly high for a solid-state technology.

Conner & Shugart

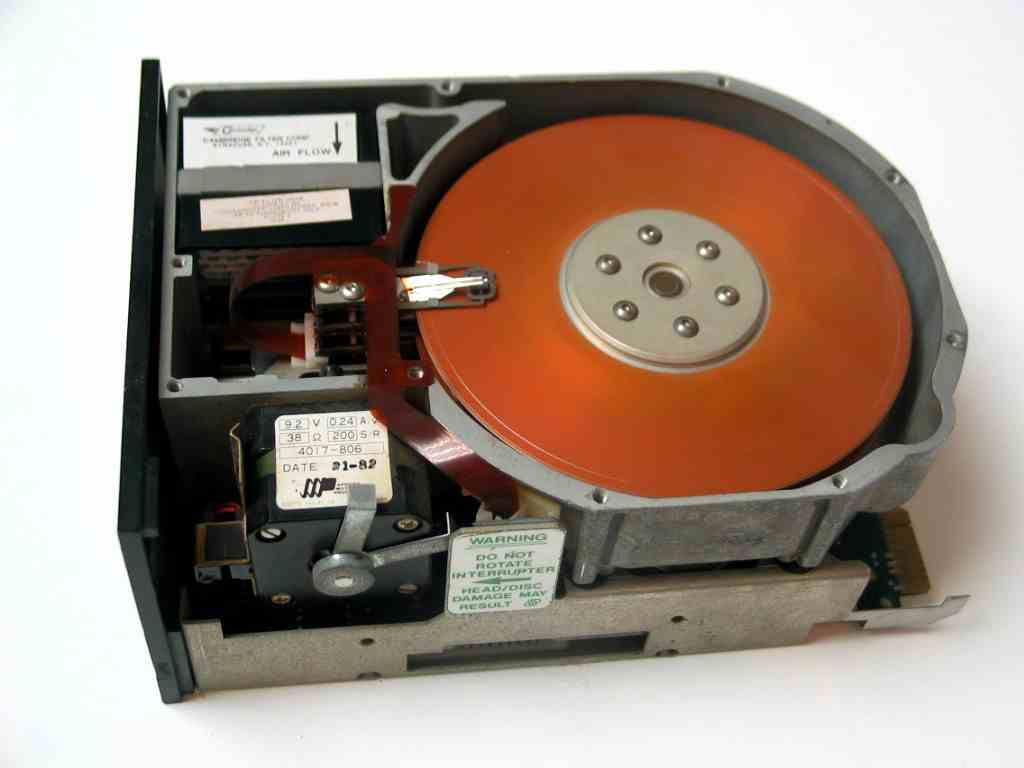

Meanwhile Finis Conner and Al Shugart, having enjoyed some success as Shugart Associates with 8″ floppy and fixed disks, in 1979 formed a startup to produce 5.25″ fixed disks for the emerging personal computer industry. Shugart Technology was born, named deliberately in the expectation of some free publicity from Shugart Associates owner Xerox.

Less than a year after incorporation, they led the storage industry with the introduction of the micro-Winchester ST-506, the first 5.25″ form factor hard drive. With 5 MB usable capacity, it immediately provided a problem for bubble technology – and DEC (absorbed by Compaq in 1998) provided Shugart with their first major order, ST-506 drives being destined for its Rainbow PC in a deal apparently negotiated over cocktails and written on a napkin (source).

Disk vs Bubble

The limitations of MBM were, by 1980, becoming clear. Whilst requiring complex controller logic similar to that of a hard disk, it was power hungry and slow in comparison: Intel’s iSBC254 bubble memory storage board needed 32W per ½MB, had a 48ms access time, burst data rate of 48KB/s and a physical volume of 50cu.in.

In contrast, the ST-506 drive boasted 10x the capacity in a package about 3x the volume, had 10x the burst data rate, and needed less than a tenth of the power per KB. The death-knell for bubble though came when, setting the pace of capacity expansion we’ve expected since, what was by then Seagate produced the 10MB ST-412 in 1981.

Originally to be named ST-512, the drive heads were changed to thin-film type and name updated to ST-412 according to a comment on theregister, but either way the significance in vintage computing is simple: it was selected by IBM for it’s PC/XT 5160 (produced from 1983 to 1987), putting Seagate on track to become one of the most successful storage vendors today.

Meanwhile with bubble further compounded by poor yields and the need for gadolinium gallium garnet and highly toxic chemicals, by the early 1980s pretty much all efforts with bubble memory had been dropped.

ST-506/ST-412 Reliability

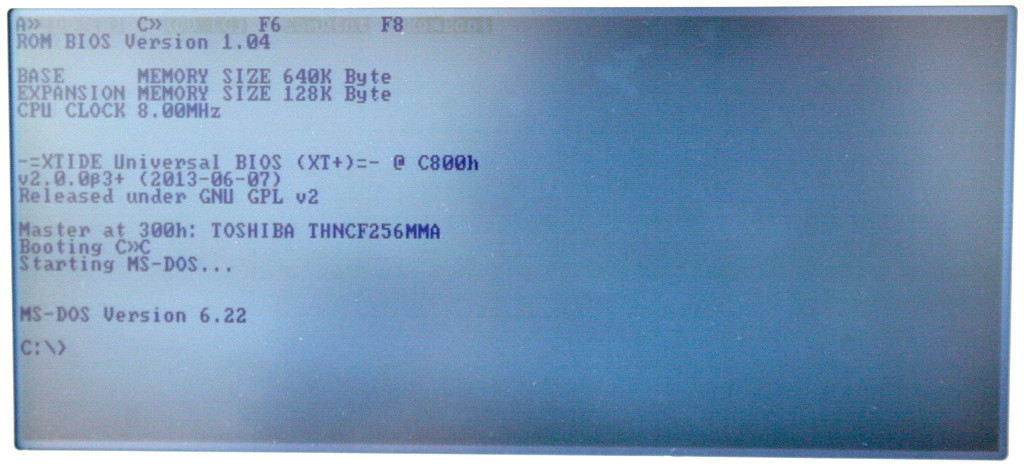

Even as of 2013, there’s no shortage of working ST-412 drives – I acquired one recently in an IBM PC/XT, which when powered on presumably for the first time in about 20 years booted up straight-off, loading the school accounts system it still stored without a fuss.

Running a low-level format (using the IBM XT Diagnostics disk – the formatter is hidden away in the diagnostics menu under fixed disk tests) gives a good indication of the state of a drive, and it completed without even the hint of a bad sector. Not bad for a 28-year old drive, especially one whose “magnetic disks have a life expectancy of 5 years” according to the service manual.

Performance

The ST506 interface used by the ST-506 and ST-412 drives was derived from the SA1000 MFM floppy interface Shugart designed in the mid 1970s, and in the PC/XT it provided 5Mbps and 17 sectors per track. Raw transfer rate is therefore about 600KB/s, but in practice much lower because an interleave was needed to allow the CPU time to collect sector data. Running my simple disk test utility the disk does about 68KB/s with the default 6:1 interleave.

Bubble Today

Bubble memory has popped up again more recently – MIT proposed a microfluidic bubble memory in 2007 (ultimately too slow) and IBM has been working on racetrack memory for some time. Whilst (as of 2013) it seems unlikely that bubble will be back any time soon, IBM Research suggests that Storage Class Memory (i.e. racetrack) could become mainstream if work on 3D NAND Flash fails to deliver.