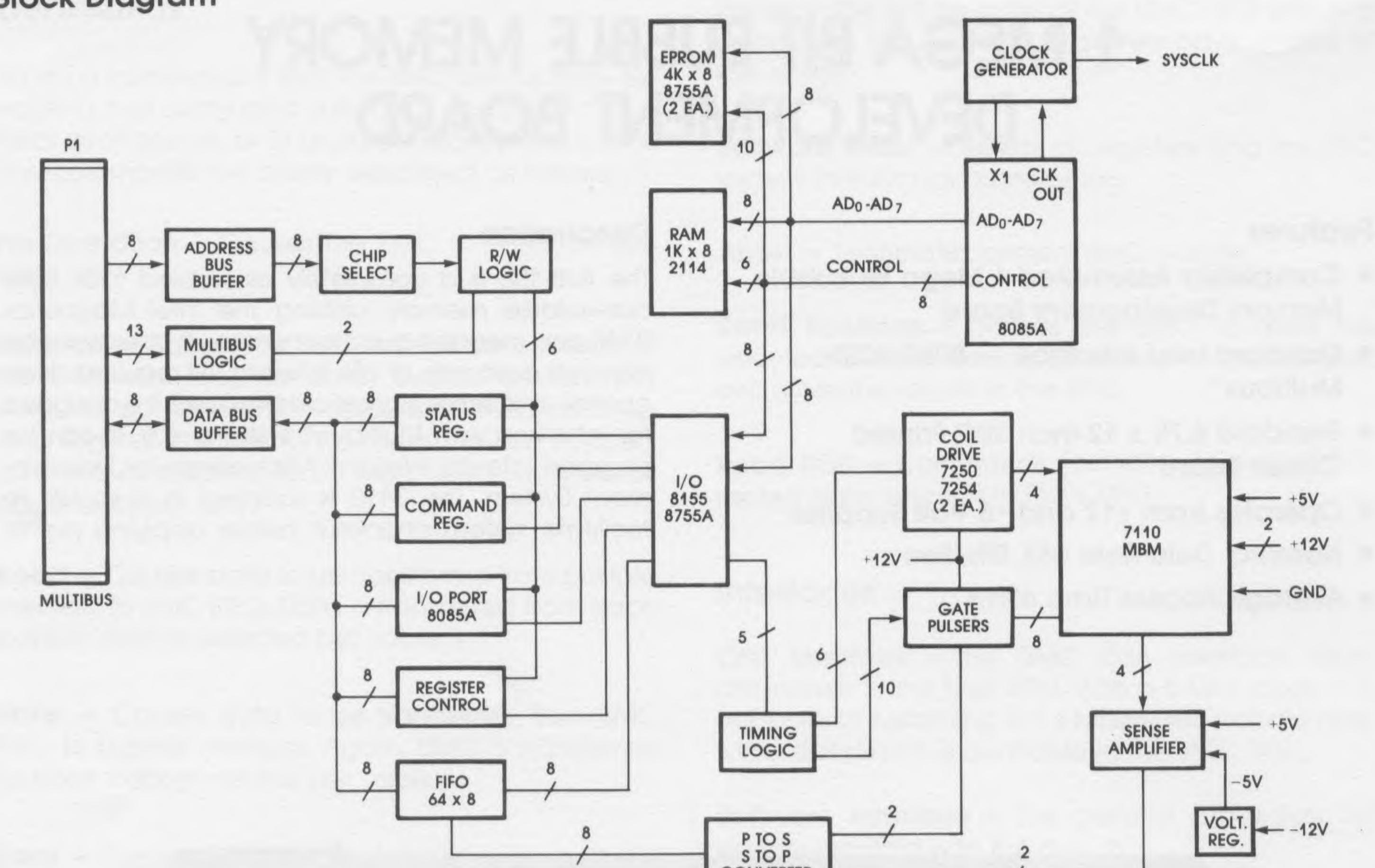

## Bubble Memory Design Handbook

#### Almac / Stroum Electronics 5811 Sixth Avenue South Seattle, Wash. 98108 Phone: 206/763-2300

MICRO SWITCH AUTHORIZED DISTRIBUTOR

## intel magnetics

# intel magnetics

# 1 Mega Bit Bube ga Bit Bubble Memory ubble Memory 1 Mega lemory 1 Mega Bit Bubble 1 Mega Bit Bubble Memory Bit Bubble Memory 1 Mega Premory 1 Mega Bit Bubb 4 Mega Bit Bubble Mem Bit Bubble Memory 1 M Memory 1 Mega P' Nega Bit Buk

## Bubble Memory Design Handbook

۵ln

©Intel Magnetics, Inc. May 1979

INTEL MAGNETICS, INC. ASSUMES NO RESPONSIBILITIES FOR THE USE OF ANY CIRCUITRY OTHER THAN CIRCUITRY EMBODIED IN AN INTEL PRODUCT. NO OTHER CIRCUIT PATENT LICENSES ARE IMPLIED.

# intel magnetics

## **Bubble Memory Design Handbook**

#### Contents

#### Page

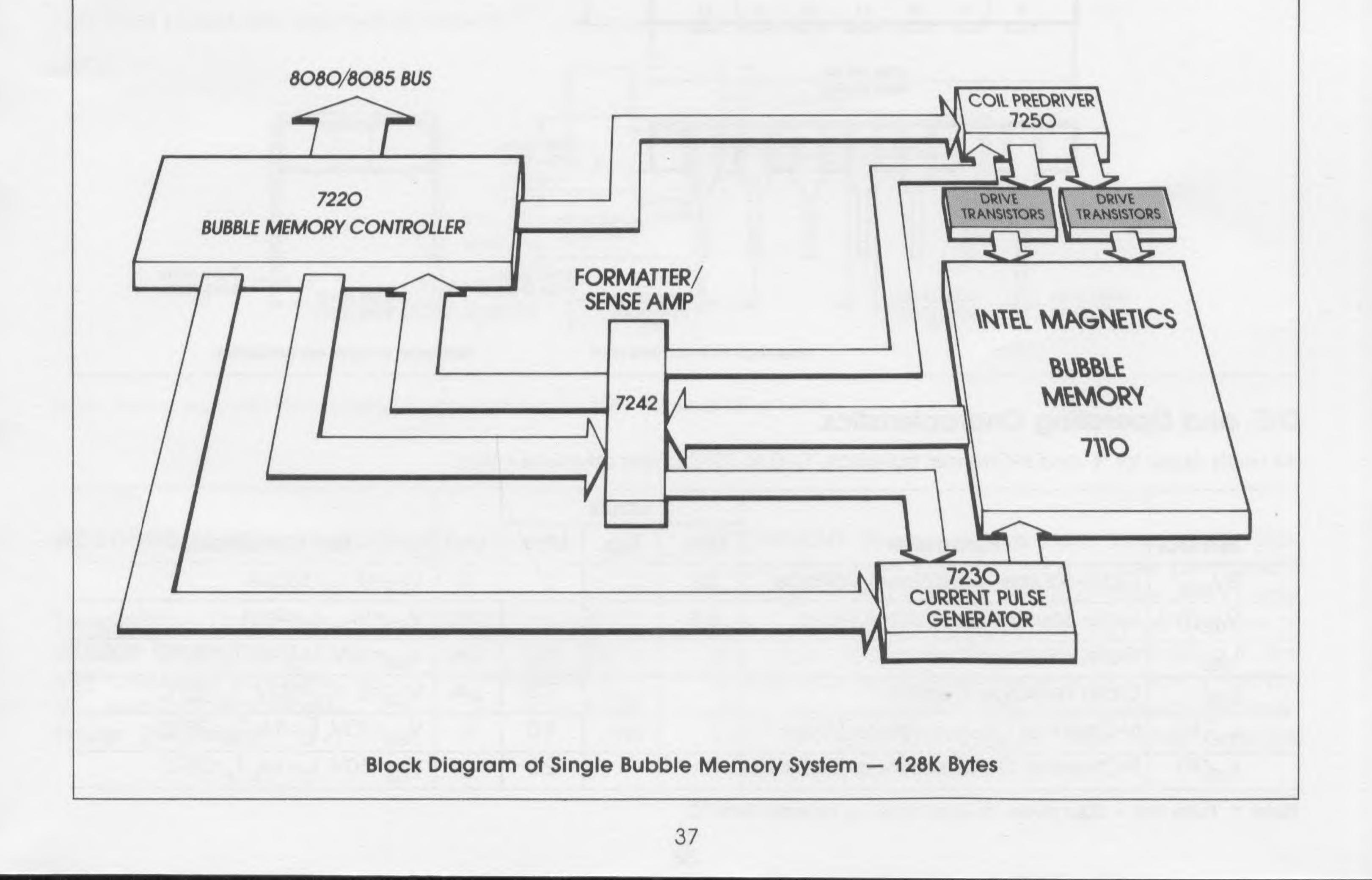

| 7110/7112     | 1 Mega Bit Magnetic Bubble Memory (MBM) 1 |

|---------------|-------------------------------------------|

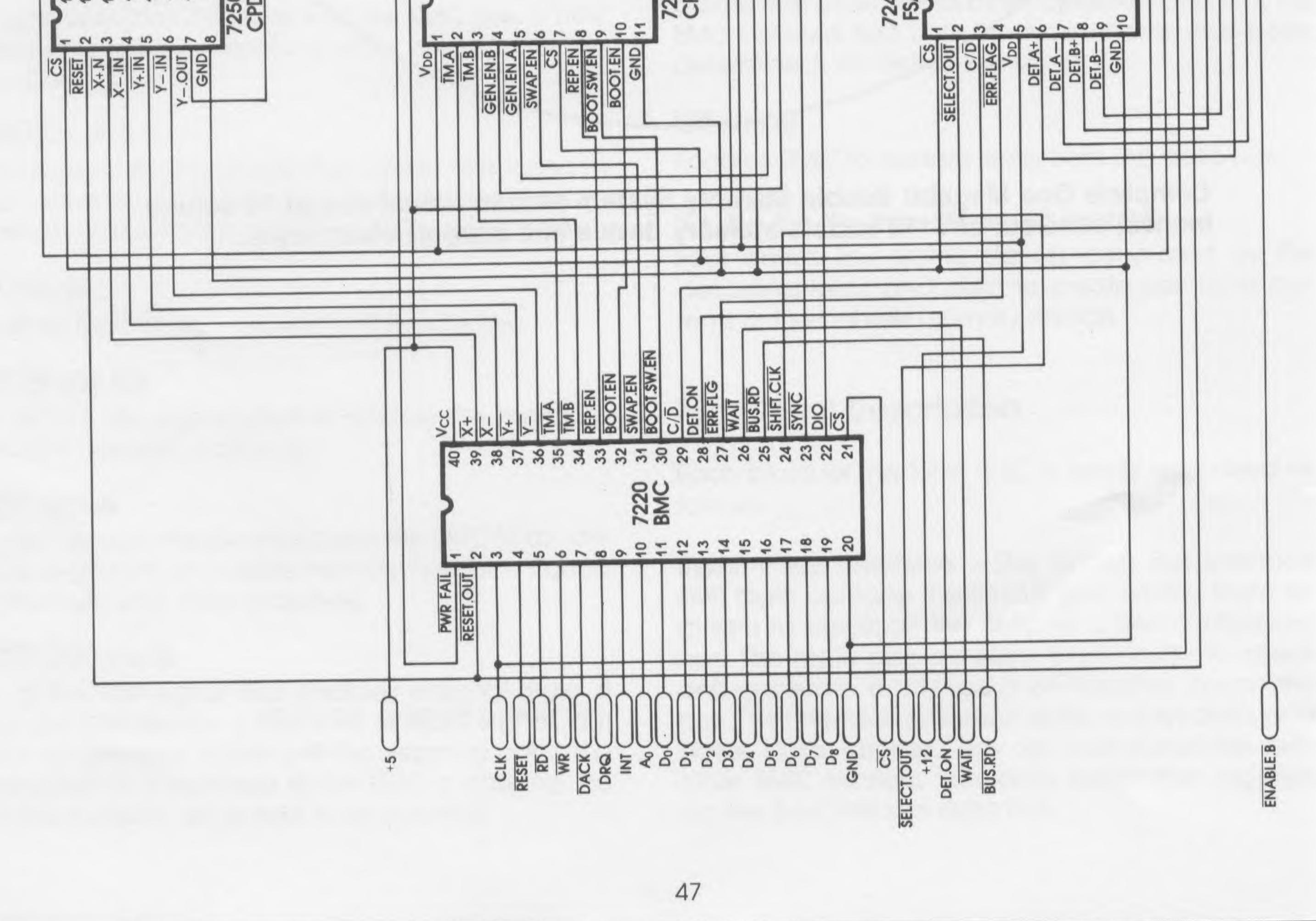

| 7220          | Bubble Memory Controller (BMC)            |

| 7230          | Current Pulse Generator (CPG)             |

| 7242          | Dual Formatter/Sense Amplifier (FSA)      |

| 7250          | Coil Pre-Driver (CPD)                     |

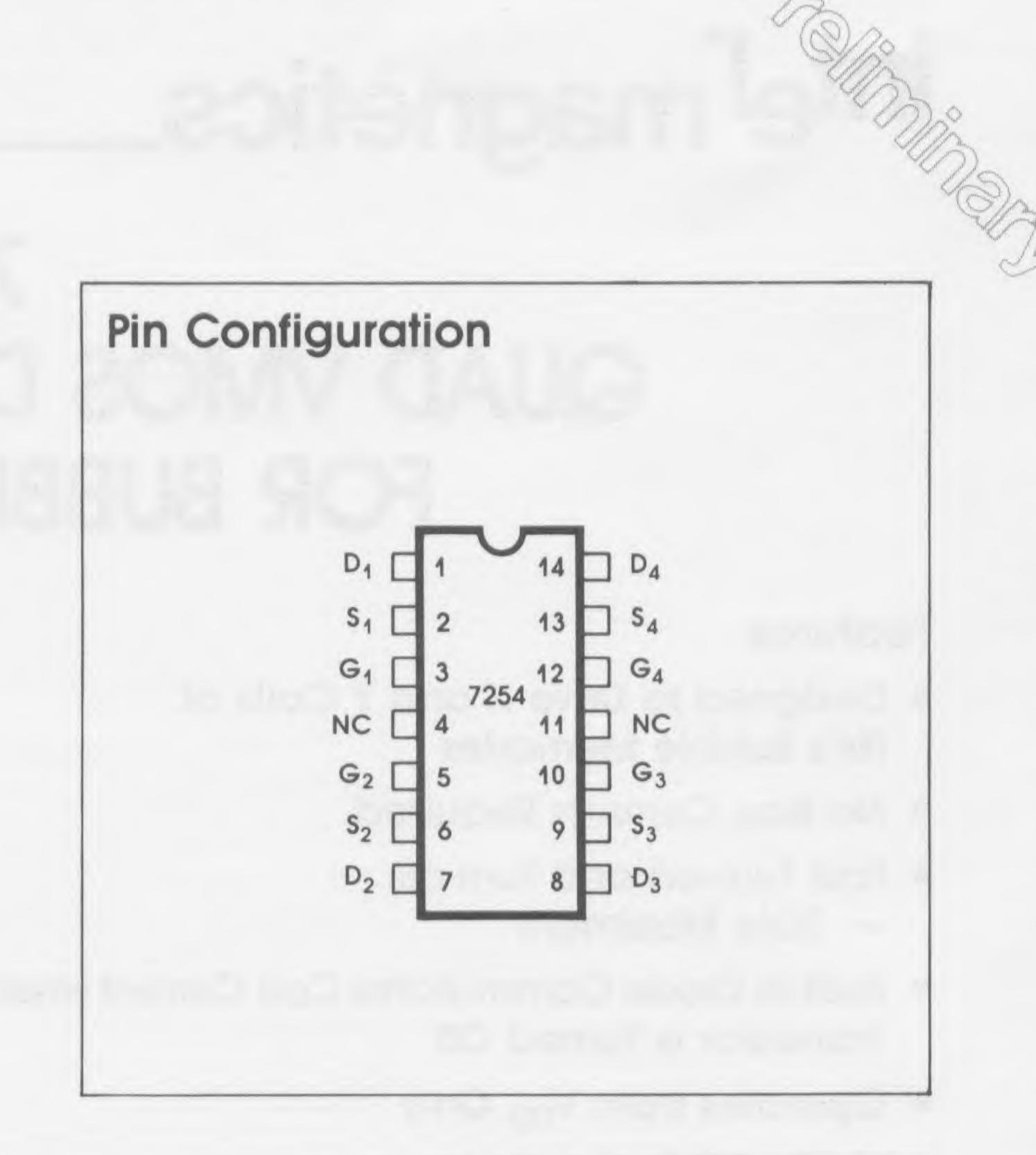

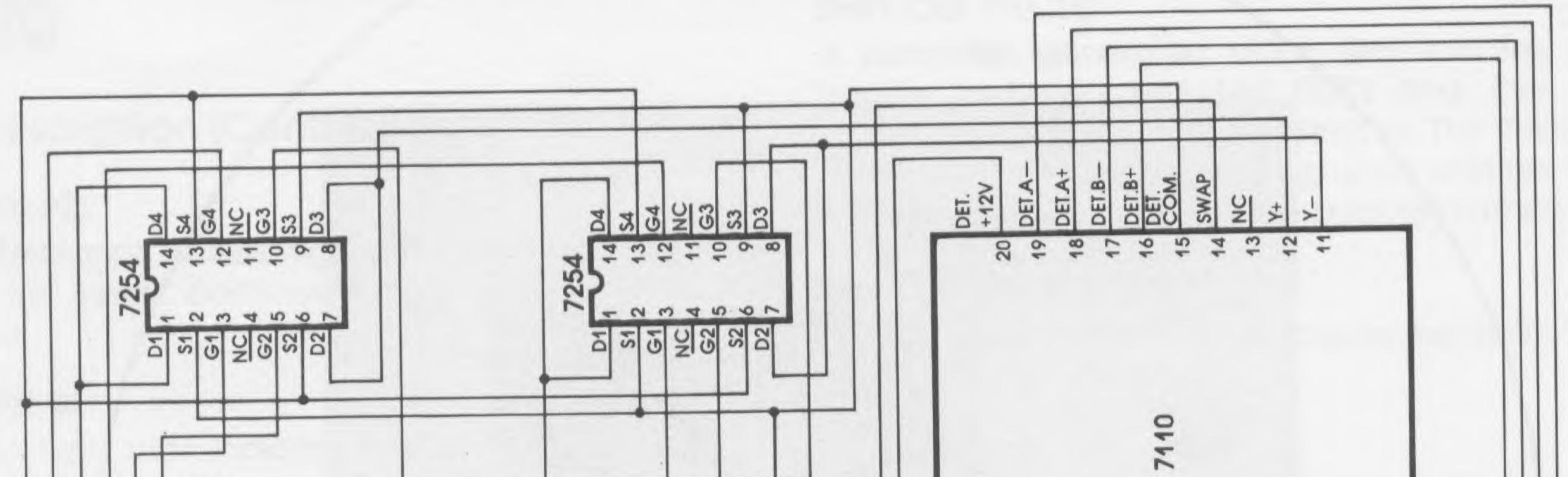

| 7254          | Quad VMOS Drive Transistors               |

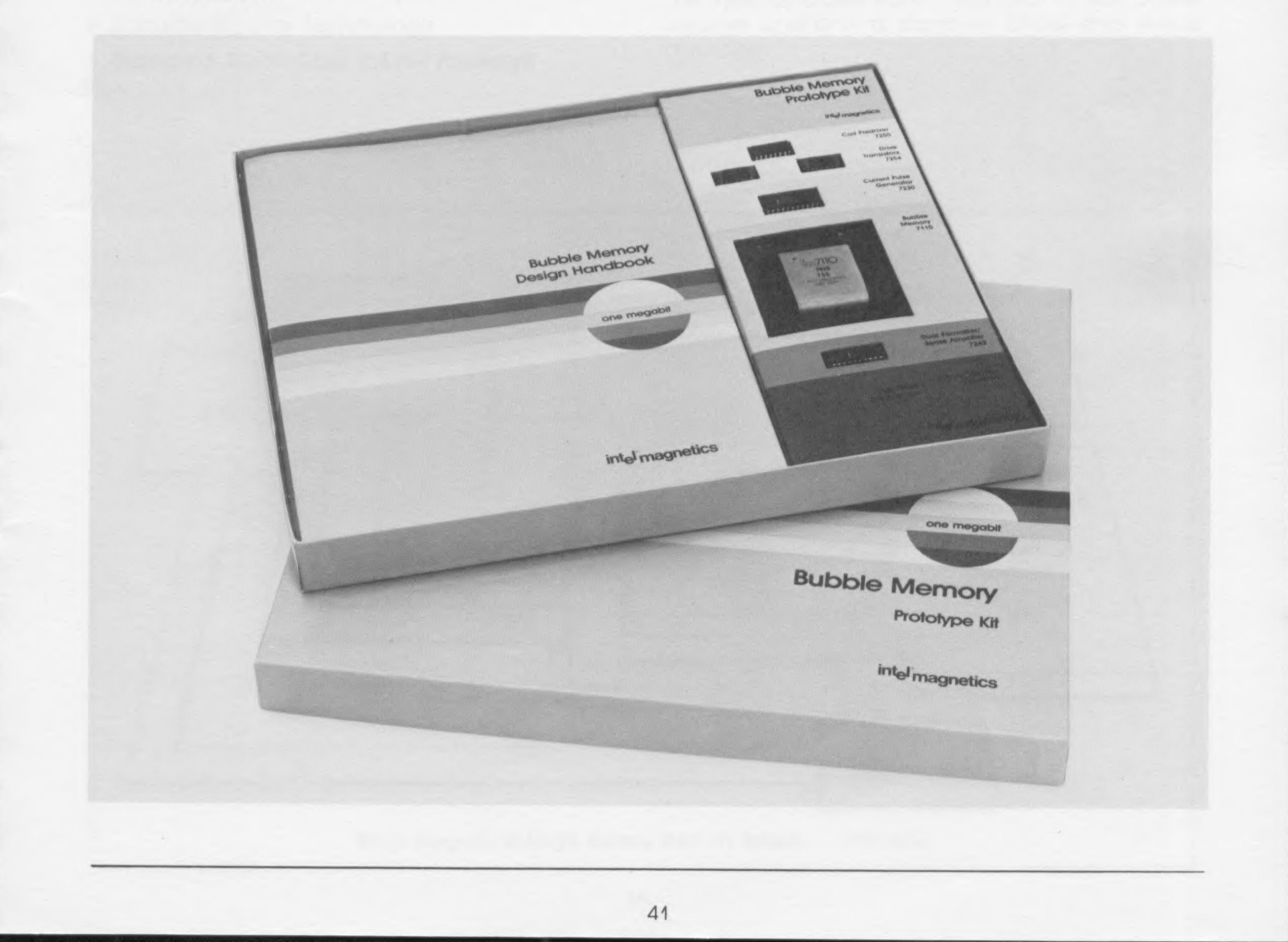

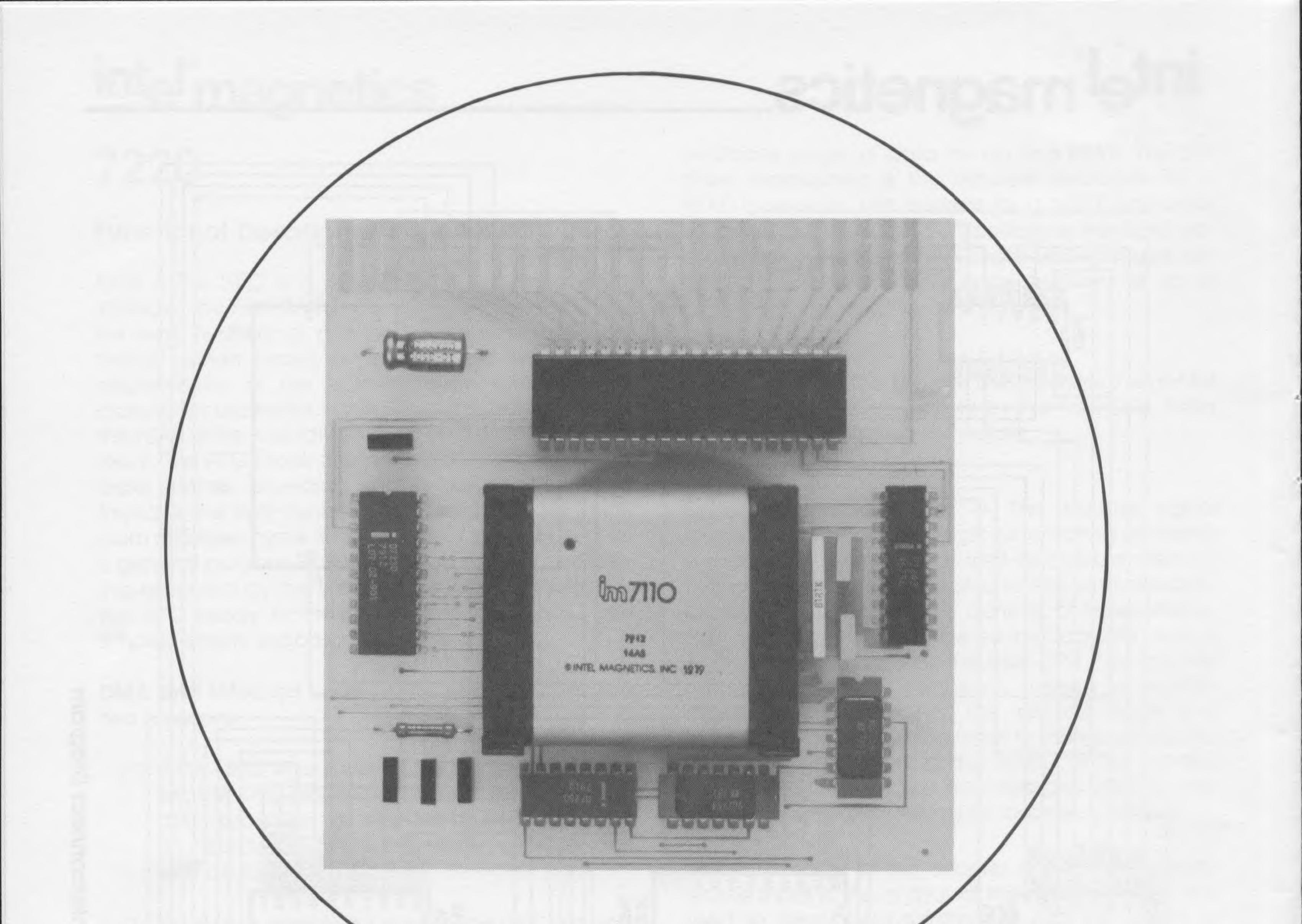

| BPK-71        | Bubble Memory Prototype Kit               |

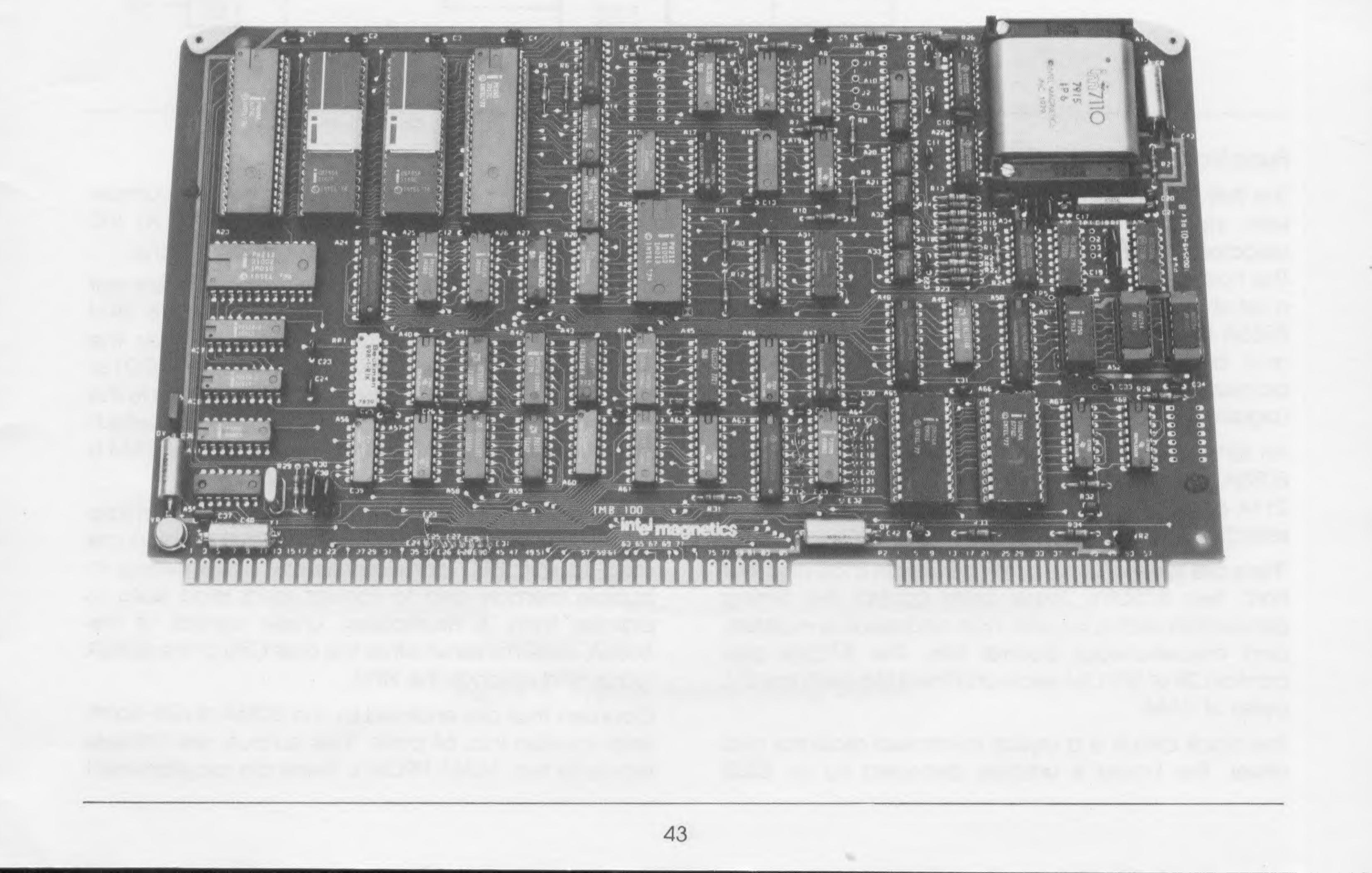

| IMB-100       | 1 Mega Bit Bubble Memory                  |

|               | Development Board                         |

| System Interc | onnect Diaaram                            |

#### Article Reprint "Megabit Bubble-Memory Chip Gets Support from LSI Family"...53

Intel Magnetics, Incorporated A Subsidiary of Intel Corporation 3000 Oakmead Village Drive Santa Clara, California 95051 Telephone: (408) 987-7700 TWX: 910-338-0026, Telex: 34-6372

# intel magnetics.

## 7110, 7112 **1 MEGA BIT BUBBLE MEMORY**

#### Features

- 1,048,576 Bits of Useable Data Storage

- Non-Volatile, Solid-State Memory

- True Binary Organization 512 Bit Page and 2048 Pages

#### Description

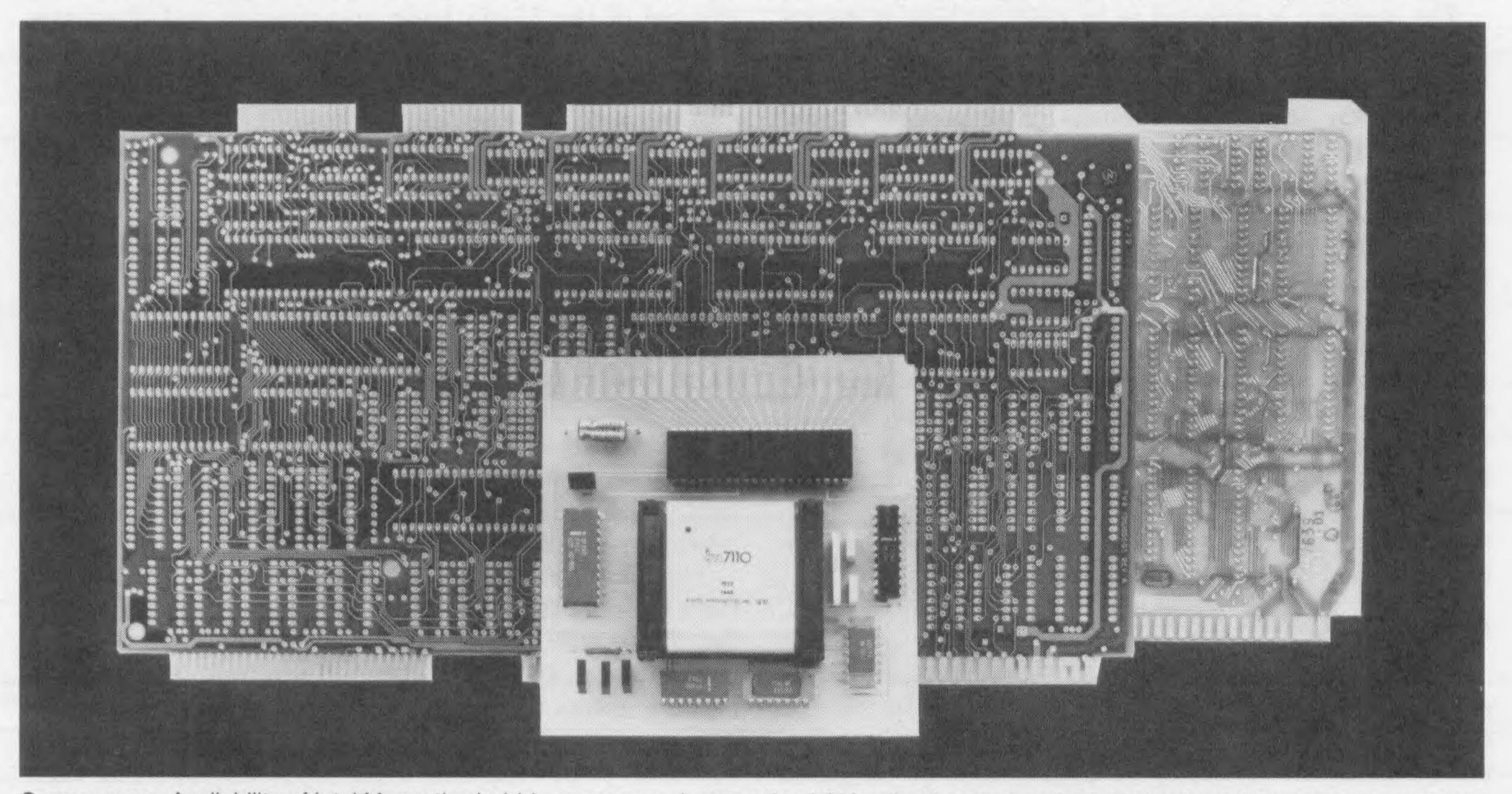

The Intel Magnetics 7110 is a very high density 1 Mega Bit non-volatile, solid-state memory utilizing the magnetic bubble technology. The usable data storage capacity is 1,048,576 bits. The defect tolerant design incorporates redundant storage loops. The gross capacity of Intel Magnetics bubble memory is 1,310,720 bits.

- Serial-Parallel-Serial Architecture

- Redundant Loops with On-Chip Loop Map and Index

- Complete Set of Interface Circuits for Ease of Use

- Controller allows 128K Bytes to 1 Mega **Byte Systems**

- Easy Paralleling or Multiplexing of IM's **Bubble Memories**

- Transparent Burst Error Correction

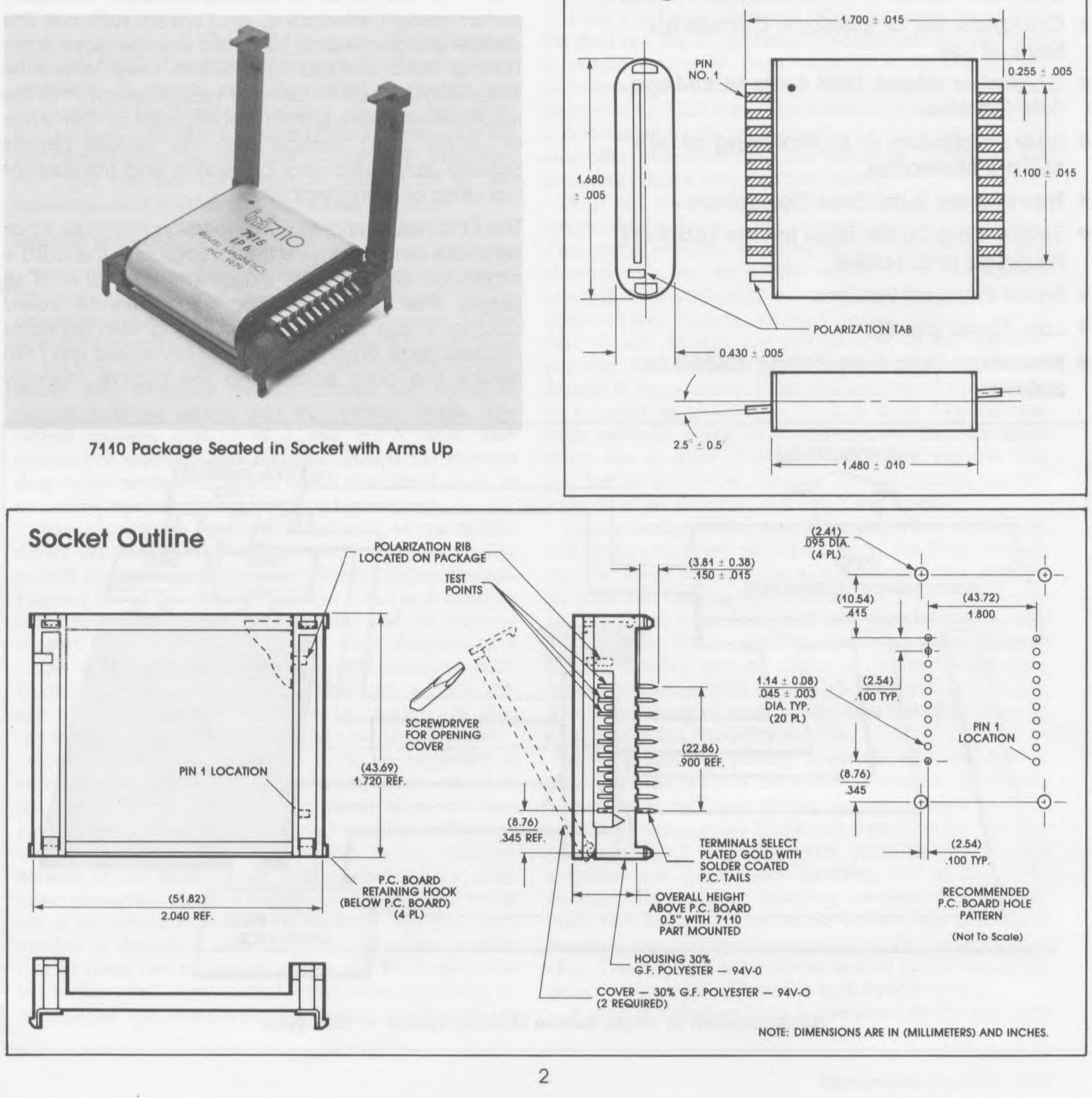

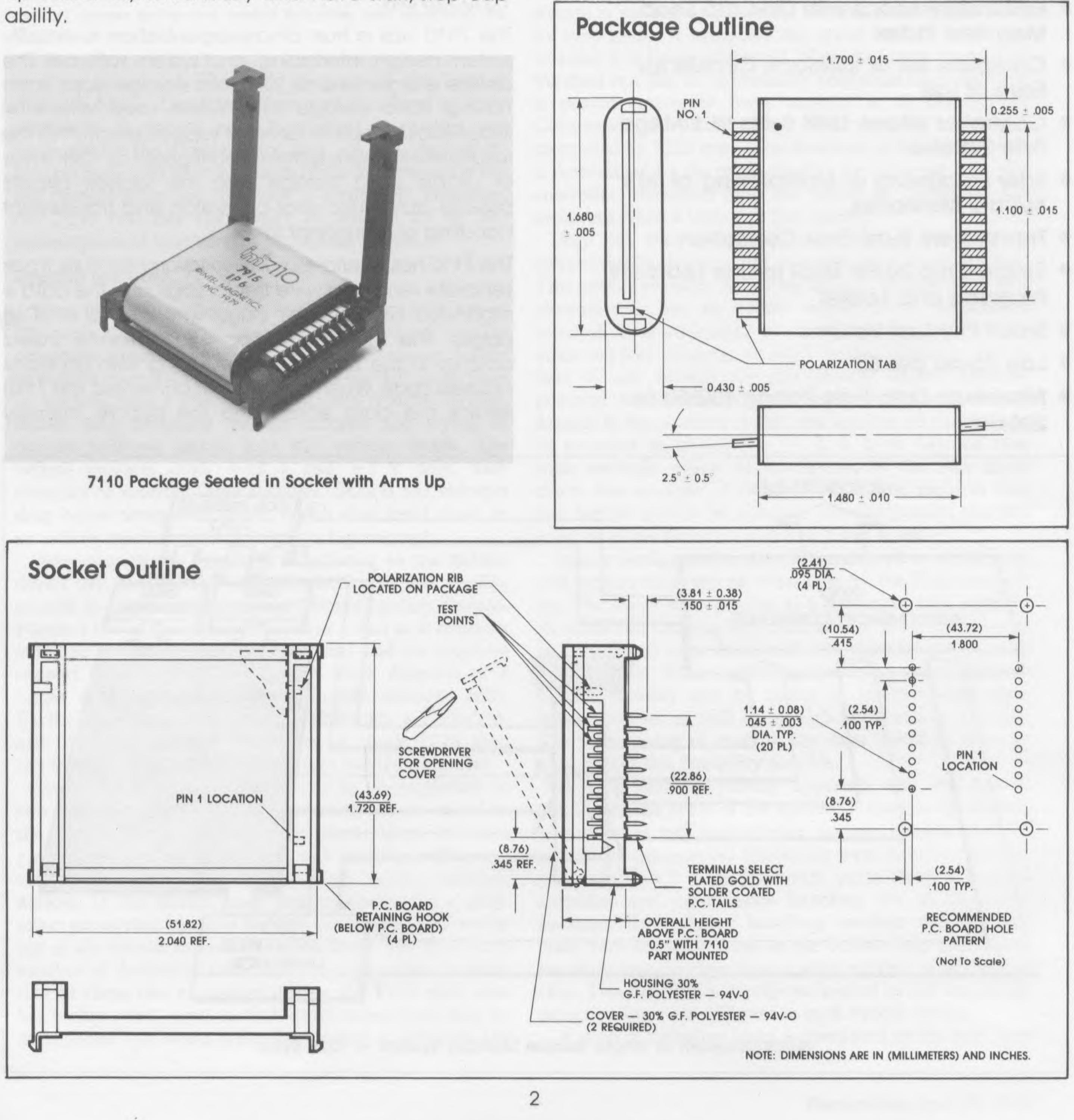

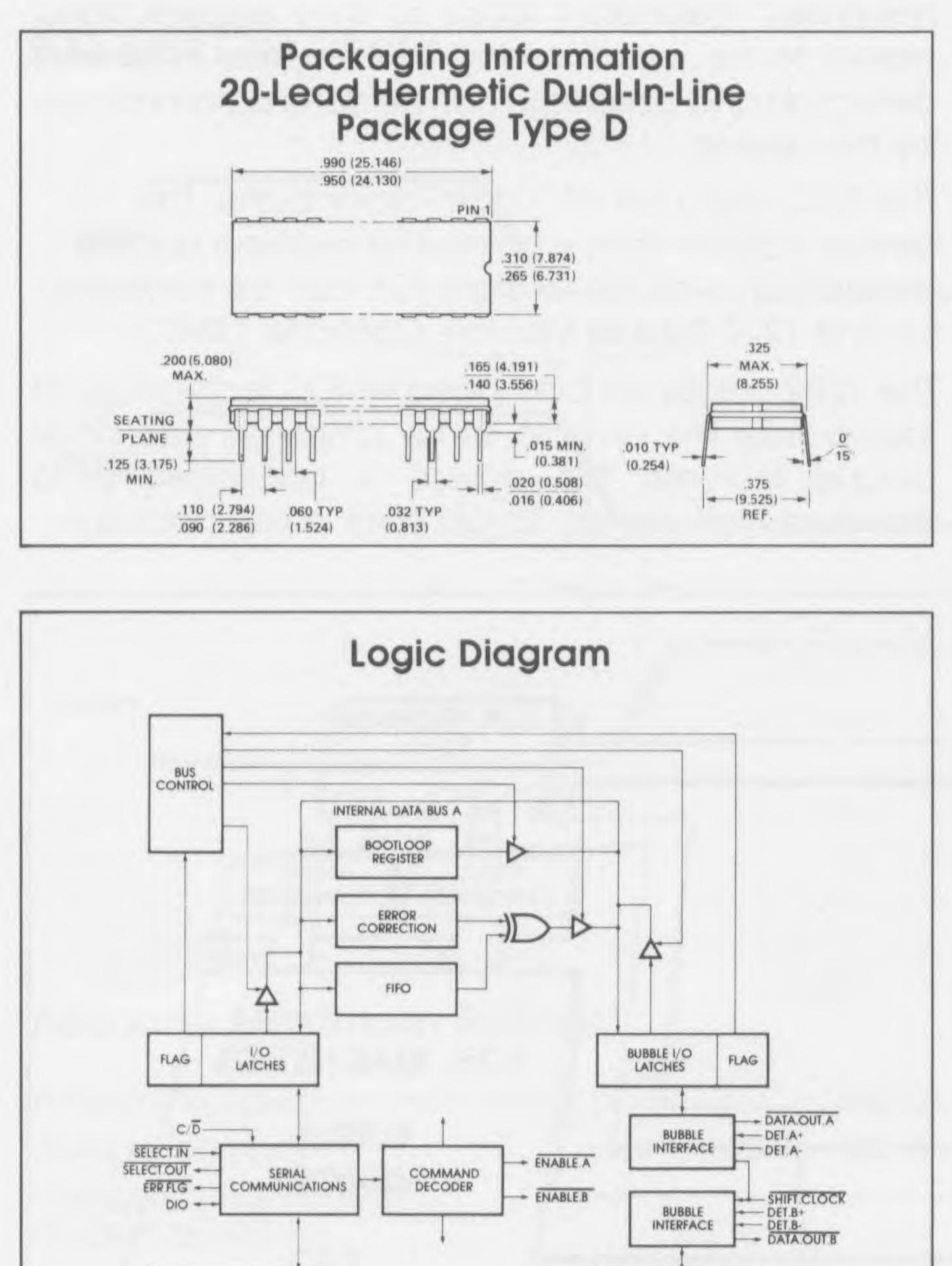

- Single Chip 20-Pin Dual In-Line Leadless Package and Socket

- Small Physical Volume

- Low Power per Bit

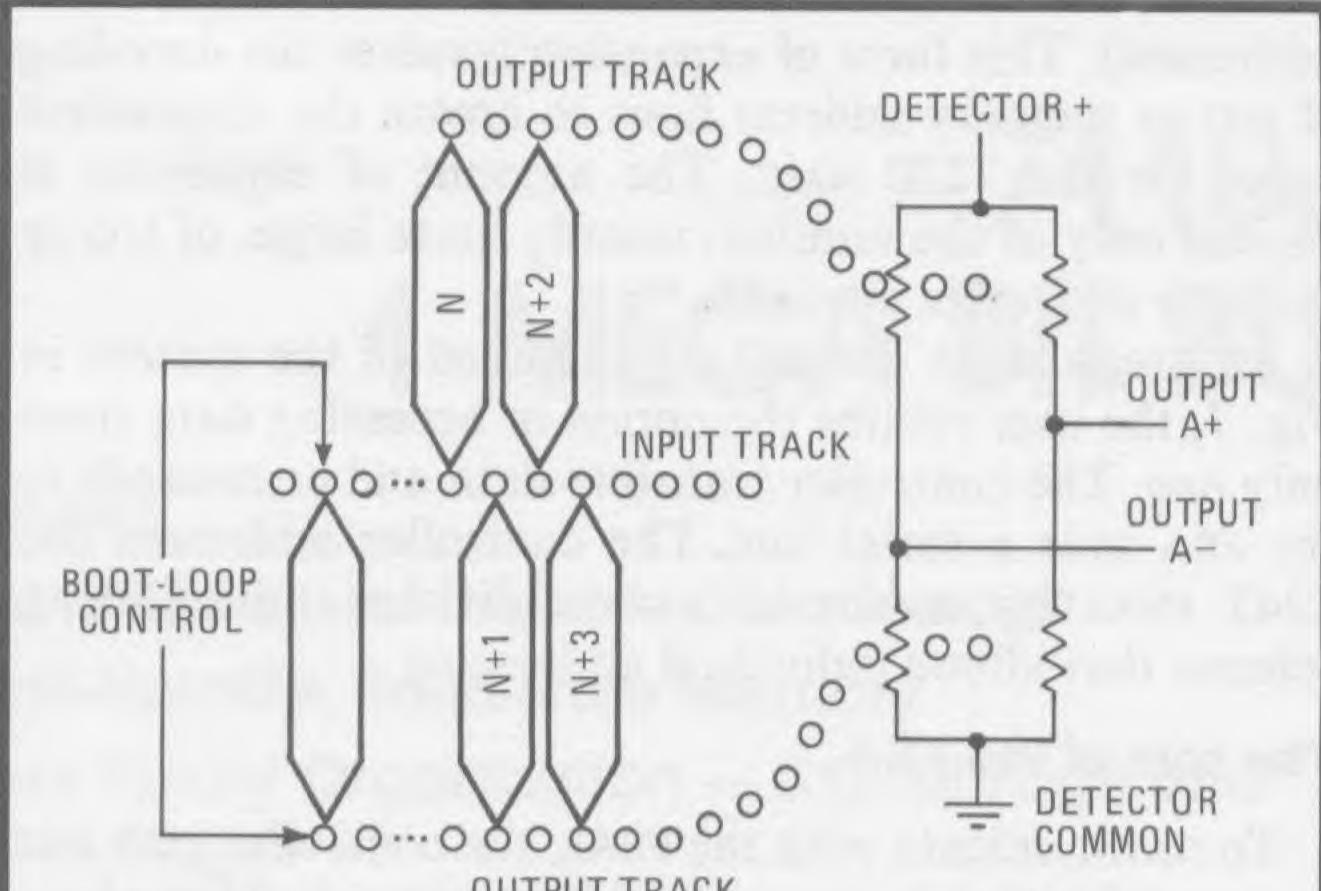

The 7110 has a true binary organization to simplify system design, interfacing, and system software. The device is organized as 256 data storage loops each 166115 having 4096 storage bits. When used with Intel Magnetics complete family of support electronics the resultant minimum system is configured as 128K Bytes of usable data storage. Also the support circuits provide automatic error correction and transparent handling of redundant loops.

The 7110 has a serial-parallel-serial architecture. It has separate read and write tracks. Logically, the data is organized as a 512 bit page with a total of 2048, 576 pages. The redundant loop information is stored on-chip in the bootstrap loop along with an index address code. When power is disconnected, the 7110 retains the data stored and the bubble memory

Maximum Data Rate Range 100kHz to 200kHz

## 7110, 7112

#### **Description** (Continued)

system is automatically restarted when power is restored via the support electronics.

The 7110 is packaged in a dual in-line leadless package complete with permanent magnets and coils for the in-plane rotating field. In addition, the 7110 has a magnetic shield surrounding the bubble memory chip to protect the data from externally induced magnetic fields.

The 7110 operating data rate is 100kHz and the 7112 operates at 200kHz. Both bubble memories can be operated asynchronously and have start/stop cap-

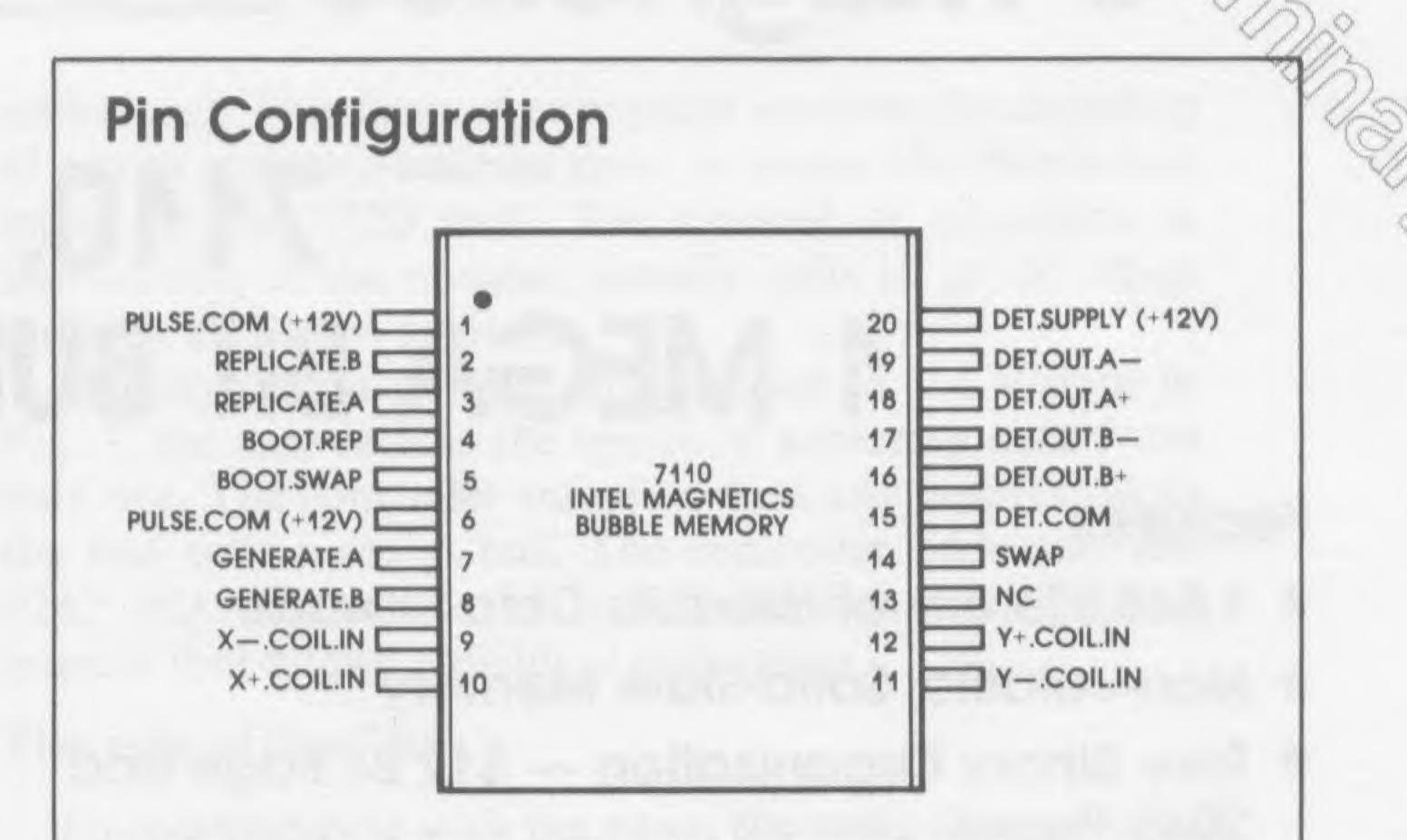

NOTE: PINS 1 AND 6 ARE NOT INTERNALLY CONNECTED AND PIN 13 SHOULD NOT BE USED AS A TIE POINT.

#### **Bubble Memory Performance Options**

|                           | 7110 | 7112 |

|---------------------------|------|------|

| Max. Data Rate (kHz)      | 100  | 200  |

| Nom. Data Rate (kHz)      | 68   | 136  |

| Rotating Field Rate (kHz) | 50   | 100  |

| Avg. Access Time (ms)     | 40   | 20   |

| Coil Voltage (V)          | +12  | +12  |

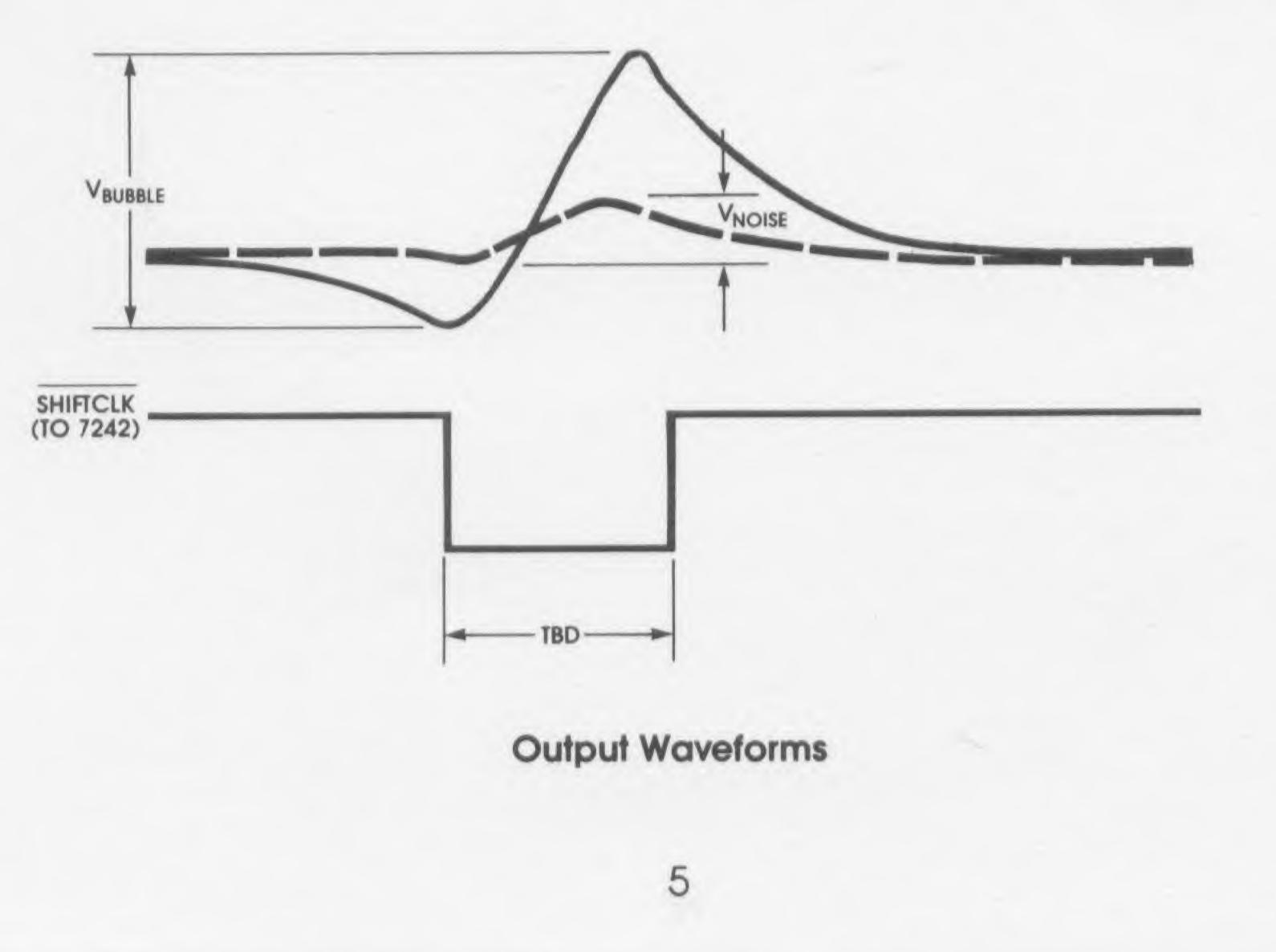

#### DET.OUT (Pins 16 through 19)

Differential pair (A+, A- and B+, B-) outputs which have signals of several millivolts peak amplitude for a '1' (bubble) or noise for a '0' (no bubble).

DET.SUPPLY (Pin 20)

+12 volt supply pin.

#### GEN.A and GEN.B (Pins 7, 8)

Two-level current pulses for writing data onto the input track.

#### PULSE.COM (Pins 1, 6)

#### **Pin Description** BOOT.REP (Pin 4)

Two-level current pulse input for reading the boot loop.

#### BOOT.SWAP (Pin 5)

Single-level current pulse for writing data into the boot loop. This pin is normally used only in the manufacture of the MBM.

#### DET.COM (Pin 15)

Ground return for the detector bridge.

#### Two unconnected +12 volt supply pins.

#### REP.A and REP.B (Pins 3 and 2)

Two-level current pulses for replicating data from storage loops to output track.

#### SWAP (Pin 14)

Single-level current pulse for swapping data from input track to storage loops.

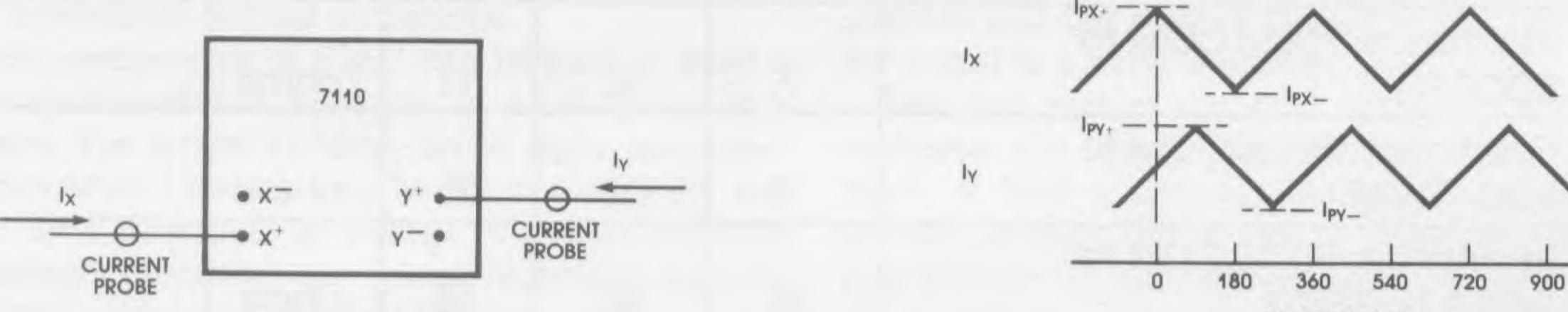

X-.COIL.IN, X+.COIL.IN (Pins 9, 10) Terminals for the X or inner coil.

Y-.COIL.IN, Y+.COIL.IN (Pins 11, 12) Terminals for the Y or outer coil.

#### D.C. and Operating Characteristics TA = 0°C to 50°C unless otherwise specified.

|                |                                                    |      | Limits |      |      |                        |

|----------------|----------------------------------------------------|------|--------|------|------|------------------------|

| Symbol         | Parameter                                          | Min. | Nom.   | Max. | Unit | <b>Test Conditions</b> |

| R <sub>1</sub> | Resistance: PULSE.COM to<br>REP.A or REP.B         | 15   | 20     | 25   | ohms |                        |

| R <sub>2</sub> | Resistance: PULSE.COM to<br>BOOT.REP               | 7    | 10     | 13   | ohms |                        |

| R <sub>3</sub> | Resistance: PULSE.COM to<br>BOOT.SWAP              | 15   | 20     | 25   | ohms |                        |

| R <sub>4</sub> | Resistance: PULSE.COM to<br>GEN.A or GEN.B         | 35   | 45     | 55   | ohms |                        |

| R <sub>5</sub> | Resistance: PULSE.COM to SWAP                      | 40   | 55     | 70   | ohms |                        |

| R <sub>6</sub> | Resistance: DET.COM to<br>DET.OUT.A+ or DET.OUT.B+ | 440  | 640    | 840  | ohms |                        |

| R <sub>7</sub> | Resistance: DET.COM to<br>DET.OUT.A— or DET.OUT.B— | 470  | 670    | 870  | ohms |                        |

| R8             | Resistance: DET.COM to<br>DET.SUPPLY               | 360  | 510    | 660  | ohms |                        |

| RX             | X Coil Resistance                                  |      | 5.2    |      | ohms |                        |

| Ry             | Y Coil Resistance                                  |      | 2.7    |      | ohms |                        |

| Lx             | X Coil Inductance                                  |      | 100    |      | μH   |                        |

| Ly             | Y Coil Inductance                                  |      | 86     |      | μH   |                        |

# intel magnetics\_

## 7110, 7112

Drive Requirements  $T_A = 0^{\circ}C$  to 50°C unless otherwise specified.

|                |                                 |        | 7110    |        |       | 7112    |        |         |

|----------------|---------------------------------|--------|---------|--------|-------|---------|--------|---------|

| Symbol         | Parameter                       | Min.   | Nom.[1] | Max.   | Min.  | Nom.[1] | Max.   | Units   |

| f <sub>R</sub> | Field Rotation Frequency        | 49.995 | 50.000  | 50.005 | 99.99 | 100.00  | 100.01 | kHz     |

| φL             | Phase Lag from Y.COIL to X.COIL | 85     | 90      | 95     | 85    | 90      | 95     | Degrees |

| Ipx+           | X.COIL Positive Peak Current    |        | 550     |        |       | 1100    |        | mA      |

| Ipx-           | X.COIL Negative Peak Current    |        | 550     |        |       | 1100    |        | mA      |

| Ipy+           | Y.COIL Positive Peak Current    |        | 690     |        |       | 1380    |        | mA      |

| Ipy-           | Y.COIL Negative Peak Current    | 1.4 0  | 690     |        |       | 1380    |        | mA      |

| PT             | Total Coil Power                |        | 1.3     | TBD    |       | TBD     | TBD    | W       |

Note: 1. Nominal values are at  $T_A = 25^{\circ}C$ .

#### **Control Pulse Requirements** Nominal values at $T_A = 25^{\circ}C$ . See Notes 1 and 2.

| Pulse                 | Amplitude (mA) | Phase of Leading Edge<br>(Degrees) | Width (Degrees) |

|-----------------------|----------------|------------------------------------|-----------------|

| GEN.A, GEN.B Cut      | 130            | 270 (Odd), 90 (Even)               | 4.5             |

| GEN.A, GEN.B Transfer | 40             | 270 (Odd), 90 (Even)               | 54              |

| REP.A, REP.B Cut      | 180            | 270                                | 4.5             |

| REP.A, REP.B Transfer | 140            | 270                                | 90              |

| SWAP                  | 140            | 180                                | 450             |

| BOOT.REP Cut          | TBD            | TBD                                | TBD             |

| BOOT.REP Transfer     | TBD            | TBD                                | TBD             |

| BOOT.SWAP             | TBD            | TBD                                | TBD             |

Notes:

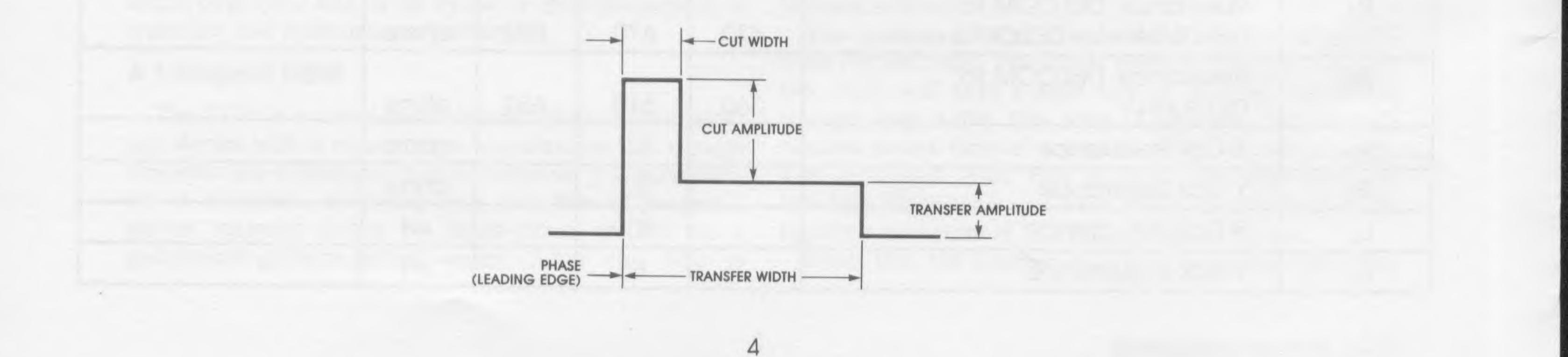

1. Pulse timing is given in terms of the phase relations as shown below. For example, a 7110 operating at  $f_R = 50.000$  kHz would have a REP.A transfer width of 90° which is 5µs.

PHASE DEGREES

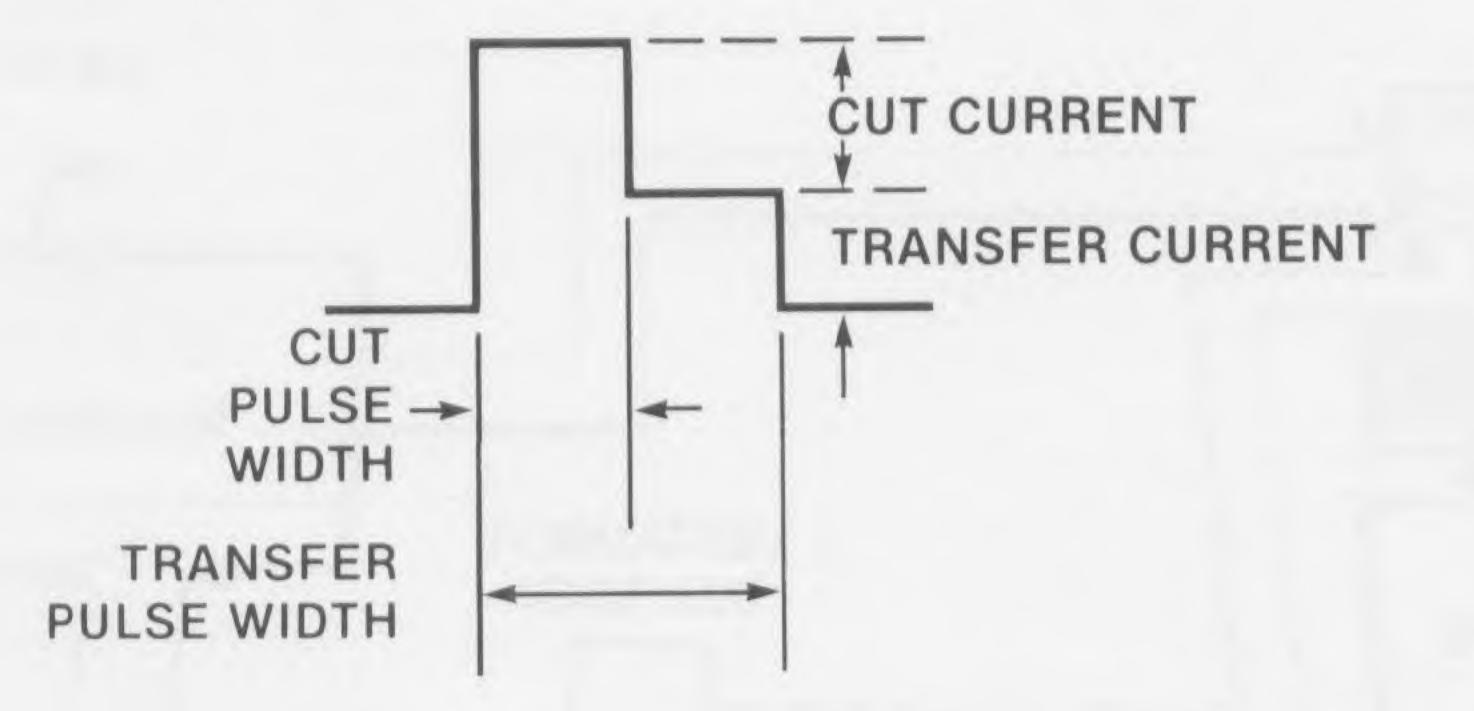

2. Two level pulses are described as shown below.

## intel magnetics\_\_\_\_\_ 7110/7112

#### Absolute Maximum Ratings\*

#### **Environmental Specifications**

|                                     | Min. | Nominal | Max. | Units    |

|-------------------------------------|------|---------|------|----------|

| Weight (Without<br>Socket)          |      | 74      | 80   | Grams    |

| External Magnetic<br>Field          |      | 40      | TBD  | Oersteds |

| Non-Operating<br>Handling Shock     |      |         | 200  | G        |

| Non-Operating<br>Vibration (2 kHz)  |      |         | 20   | G        |

| Operating Vibration<br>Up to 500KHz |      |         | TBD  | G        |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

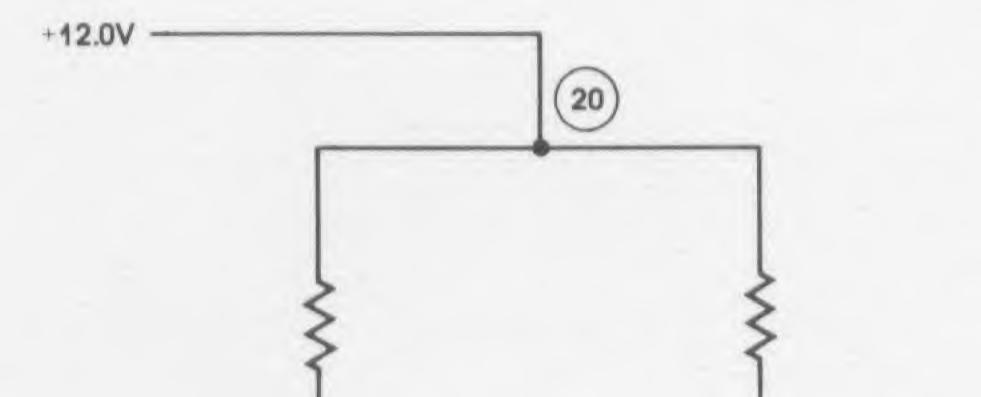

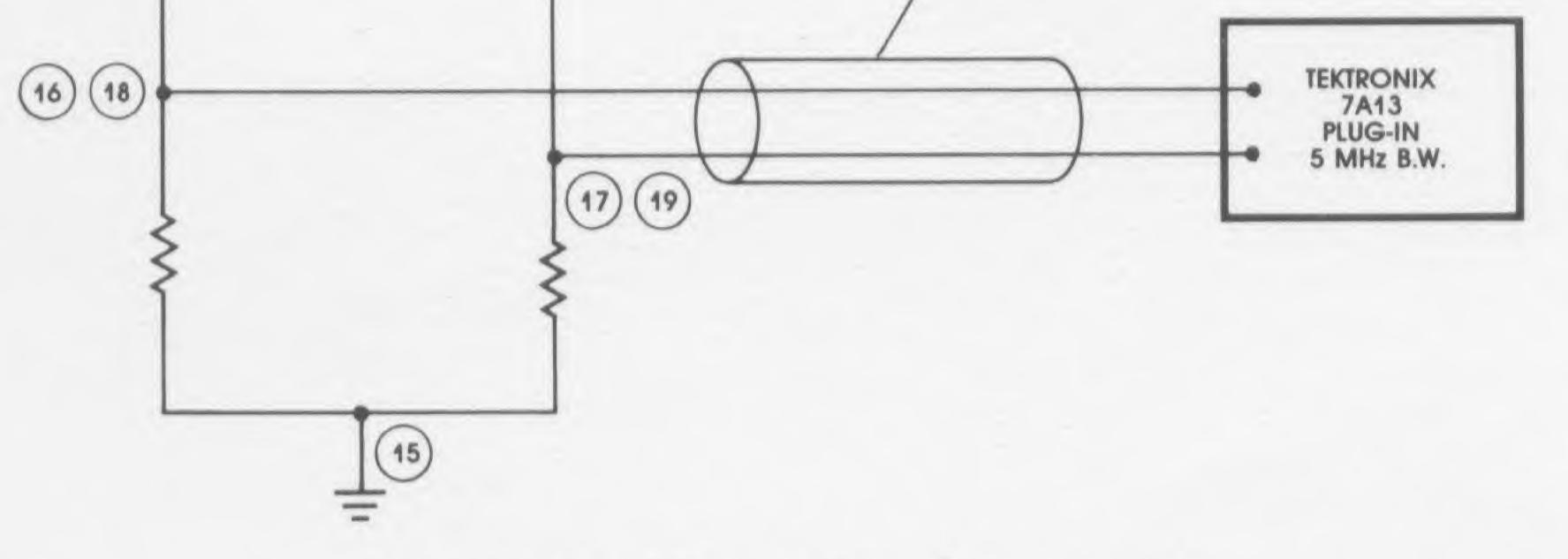

#### **Output Characteristics**

$T_A = 25^{\circ}C$  unless otherwise specified.

|         | Min. | Nom. | Max. | Units | Test<br>Conditions |

|---------|------|------|------|-------|--------------------|

| VBUBBLE | TBD  | 8.0  |      | mV    | See Figures        |

| VNOISE  |      | 1.5  | TBD  | mV    | below.             |

**BELDEN 9272 TWINAX**

Test Set-Up for Output Voltage Measurement

....

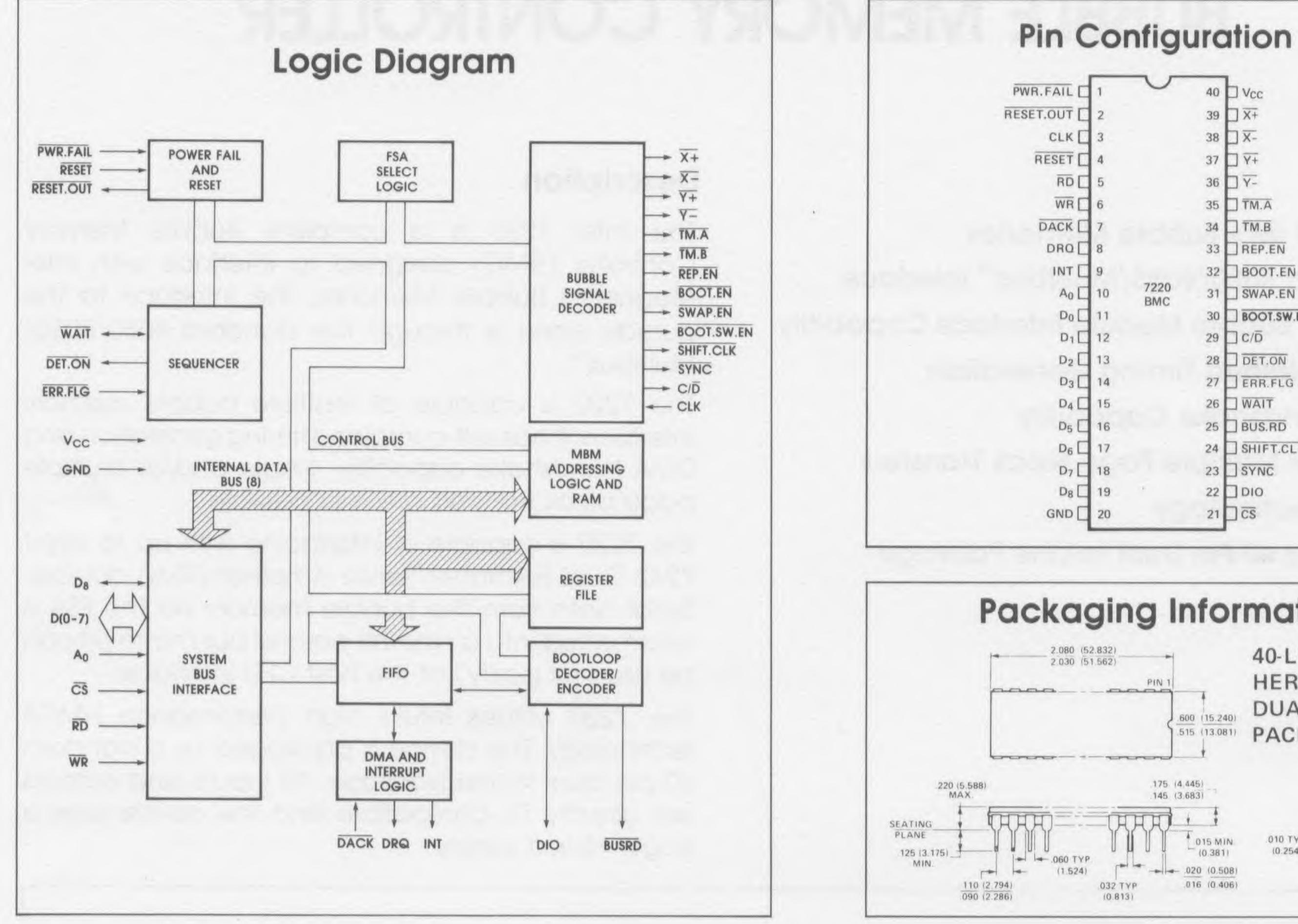

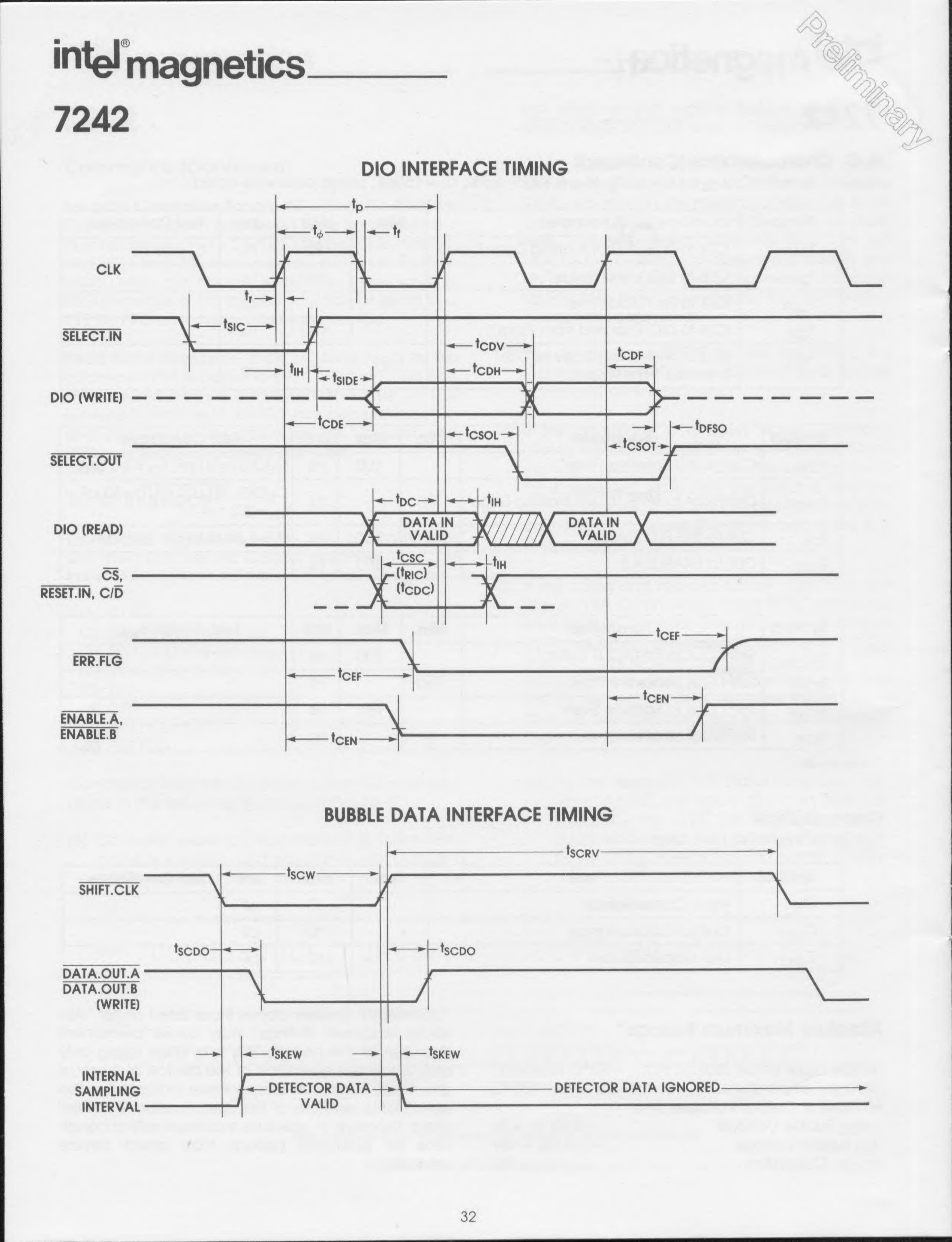

## 7220 BUBBLE MEMORY CONTROLLER

Features

Ideal for IM's Bubble Memories

#### Description

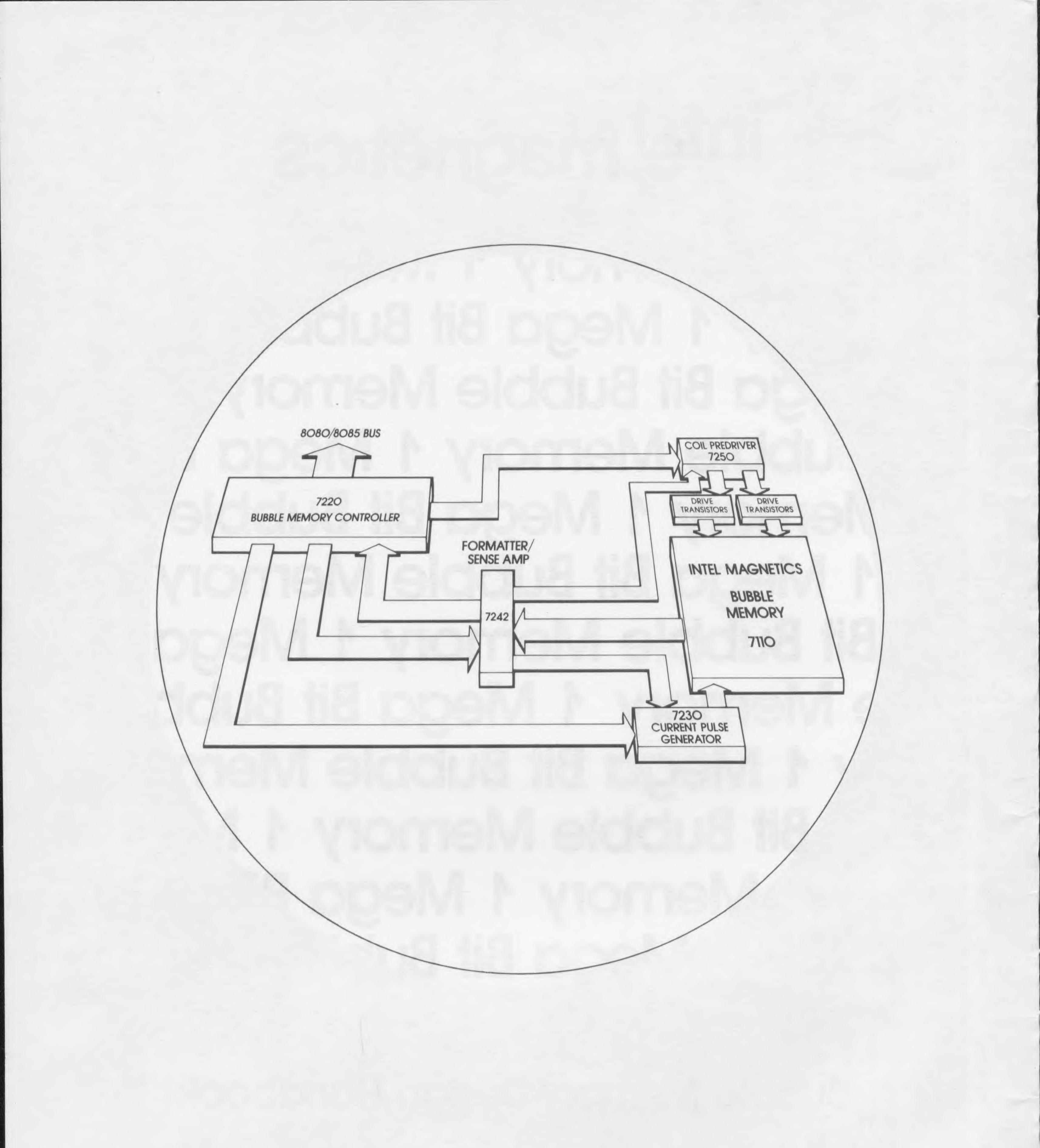

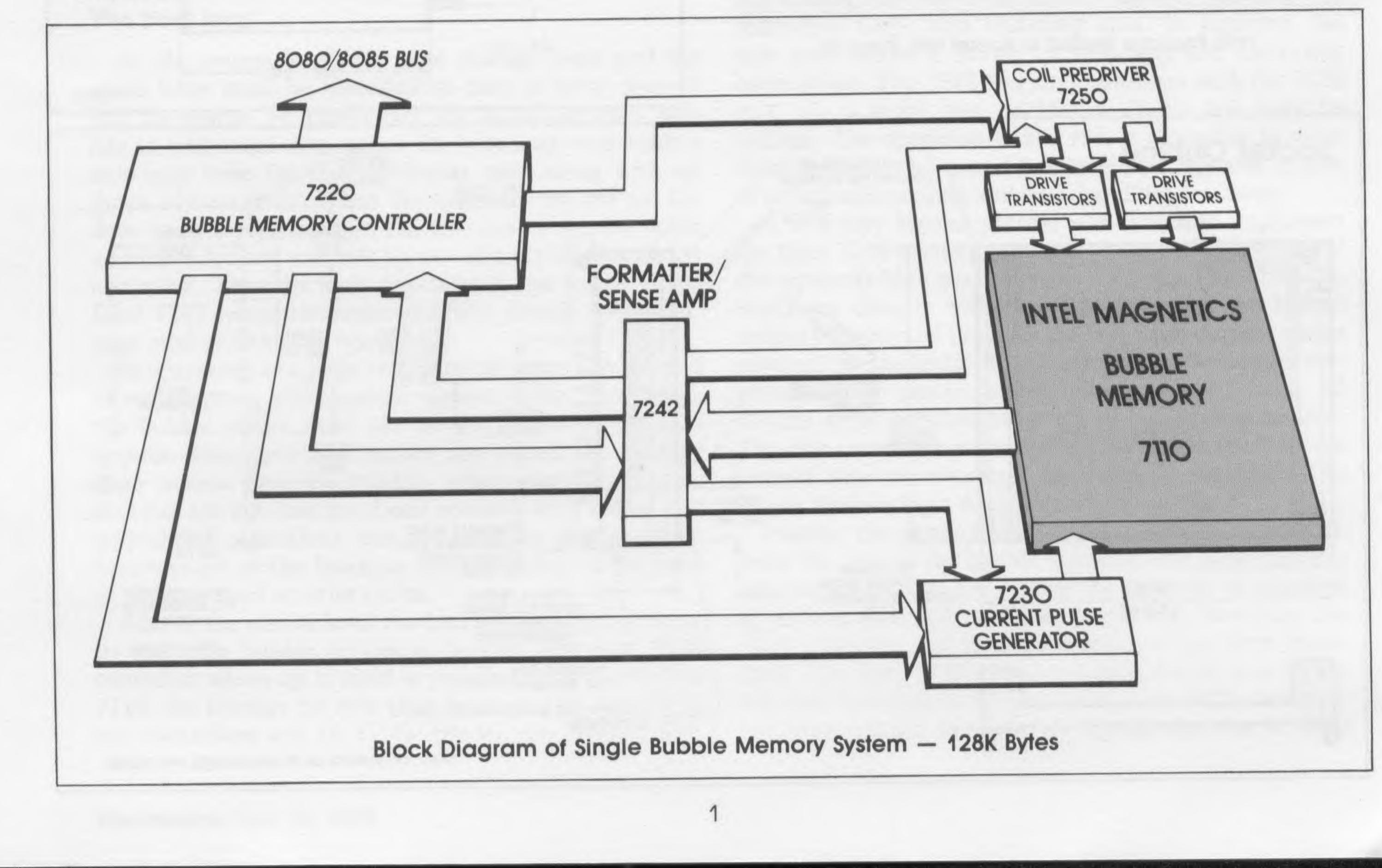

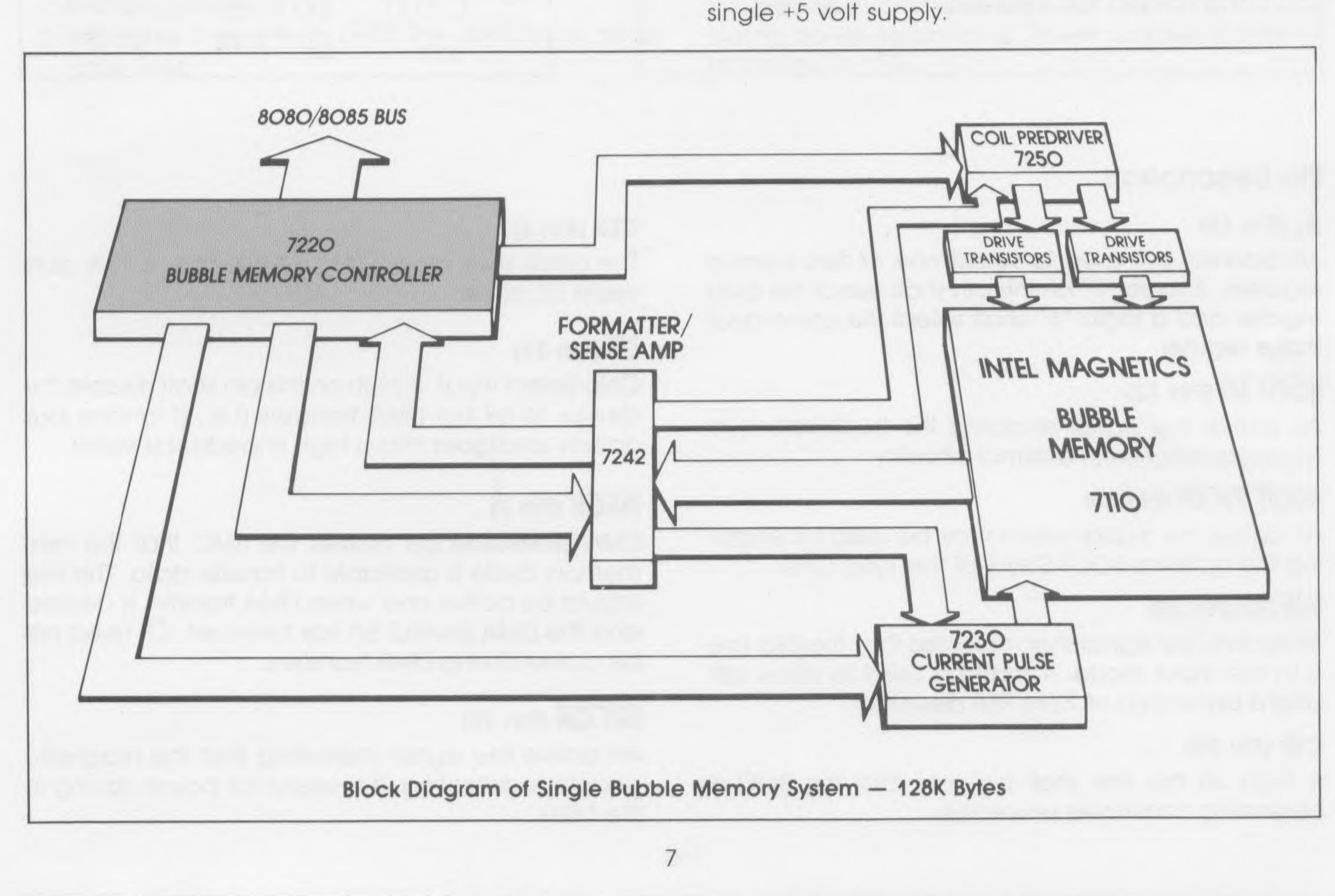

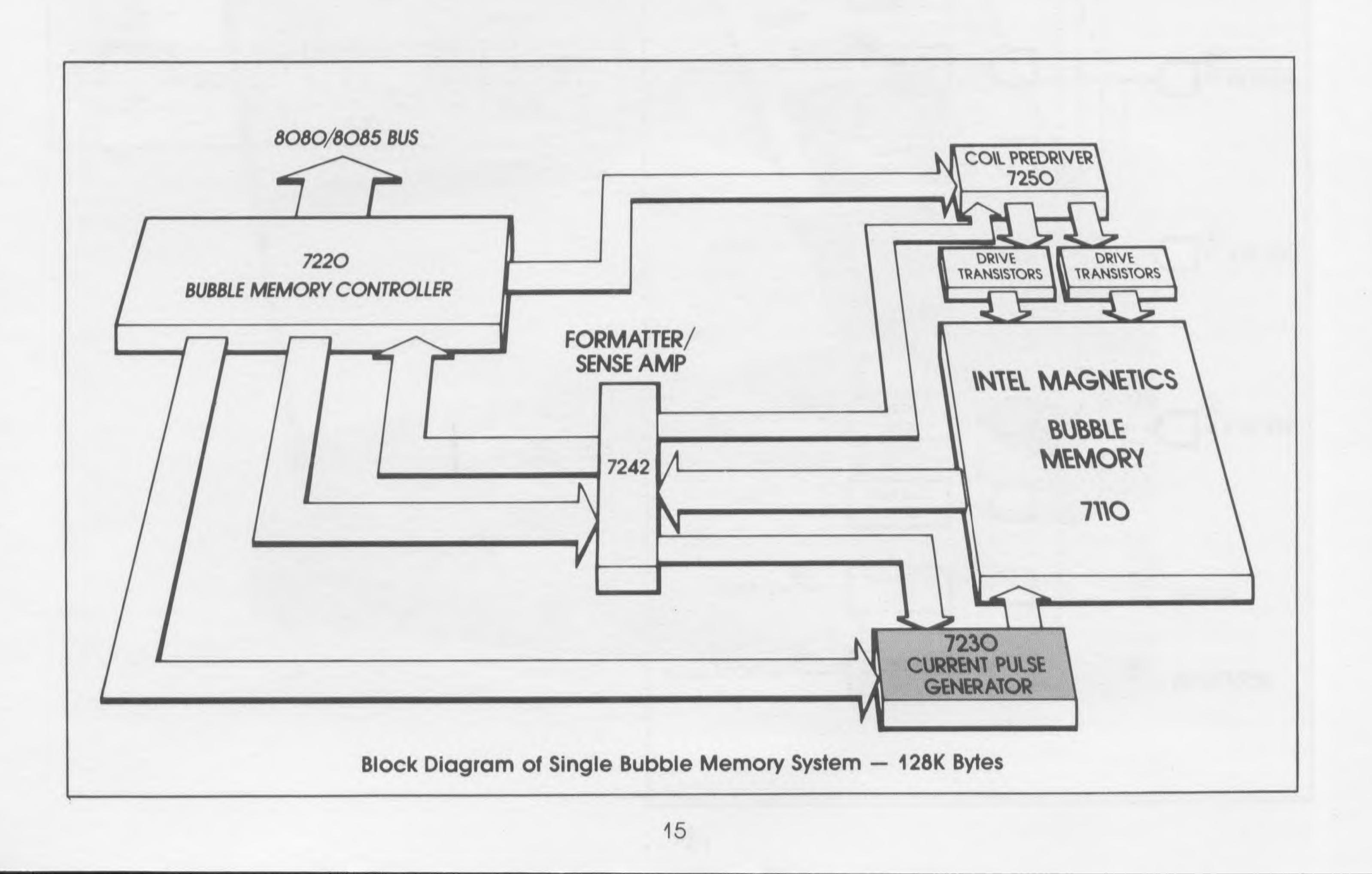

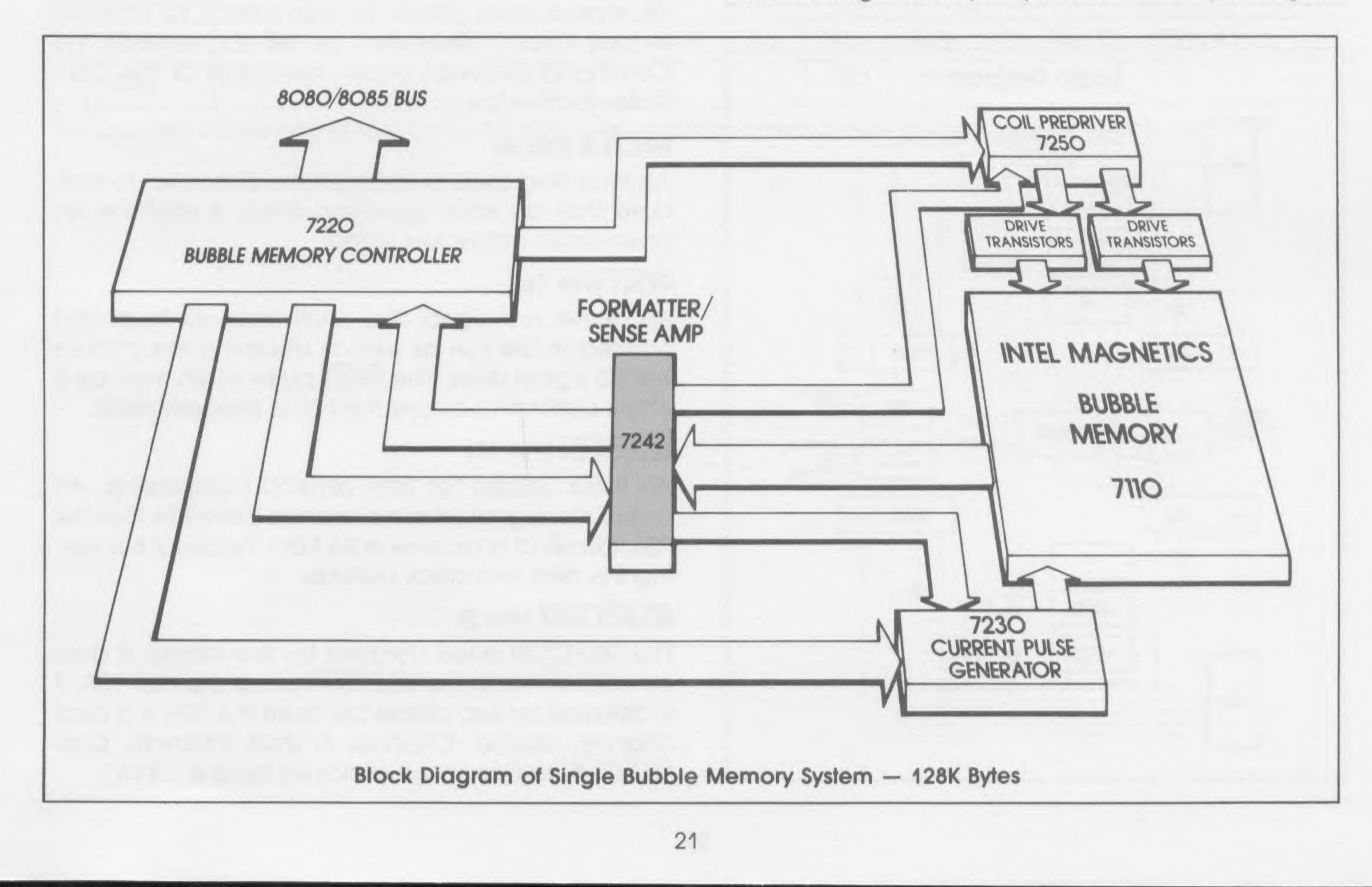

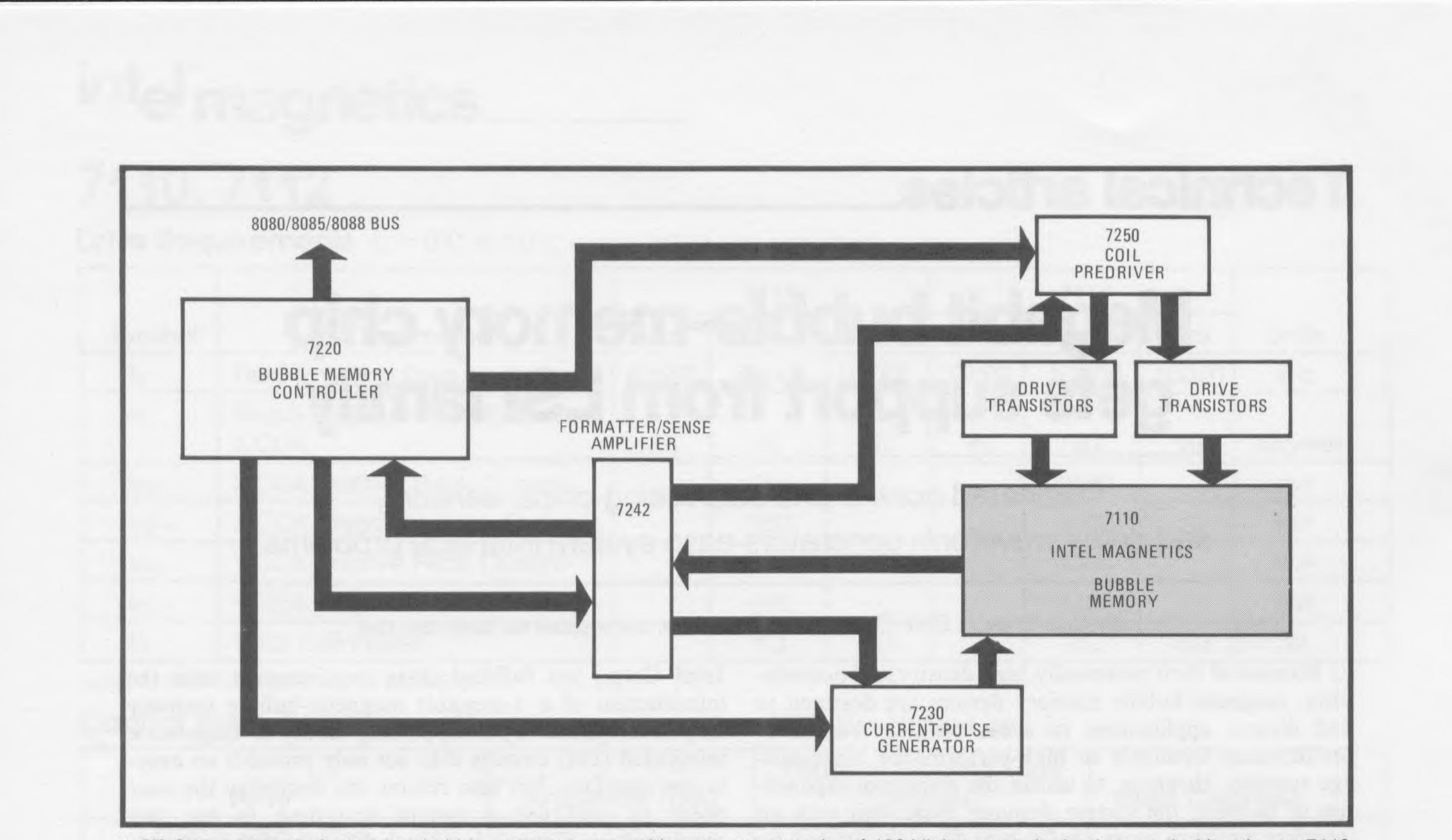

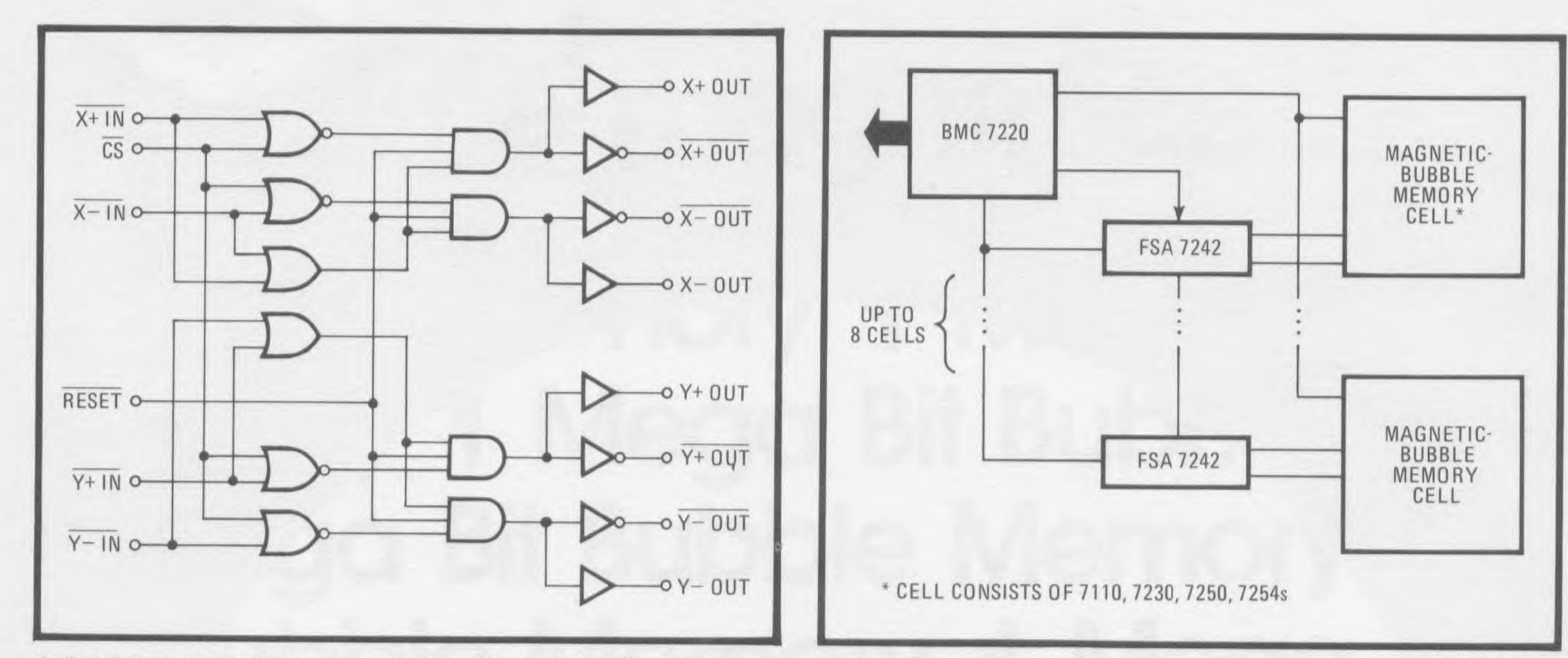

The Intel 7220 is a complete Bubble Memory Controller (BMC) designed to interface with Intel Magnetics Bubble Memories. The interface to the outside world is through the standard 8080/8085/ Multibus<sup>™</sup>.

- Standard 8080/8085/Multibus<sup>™</sup> Interface

- Multiple Bubble Module Interface Capability

- Self-Contained Timing Generation

- DMA Handshake Capability

- Single or Multiple Page Block Transfers

- HMOS Technology

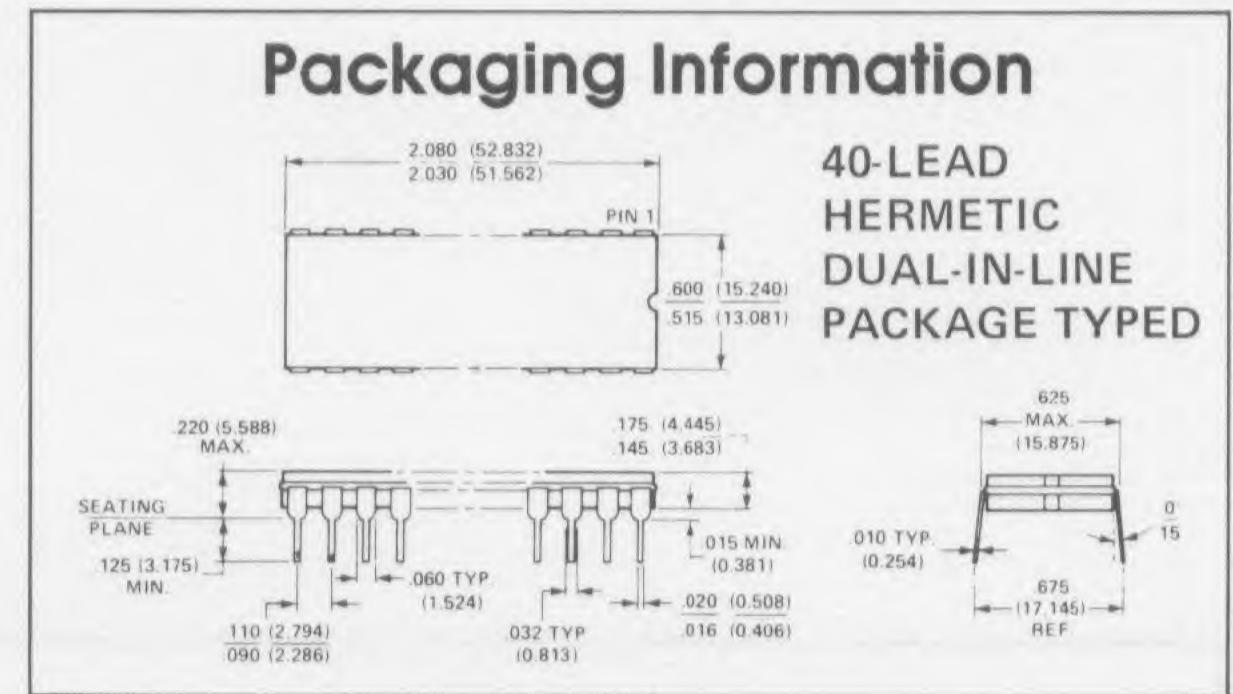

- Standard 40-Pin Dual In-Line Package

The 7220 is capable of multiple bubble memory interface. It has self-contained timing generation and DMA handshake capability. Single and/or multiple page block transfers are also possible.

The 7220 is capable of interfacing with up to eight 7242 Dual Formatter/Sense Amplifier (FSA) devices. Serial data from the bubble memory via the FSA is reformatted into a nine bit parallel bus (ninth bit can be used for parity) at the host CPU interface.

The 7220 utilizes Intel's high performance HMOS technology. The device is packaged as a standard 40-pin dual in-line package. All inputs and outputs are directly TL compatible and the device uses a single +5 walt supply.

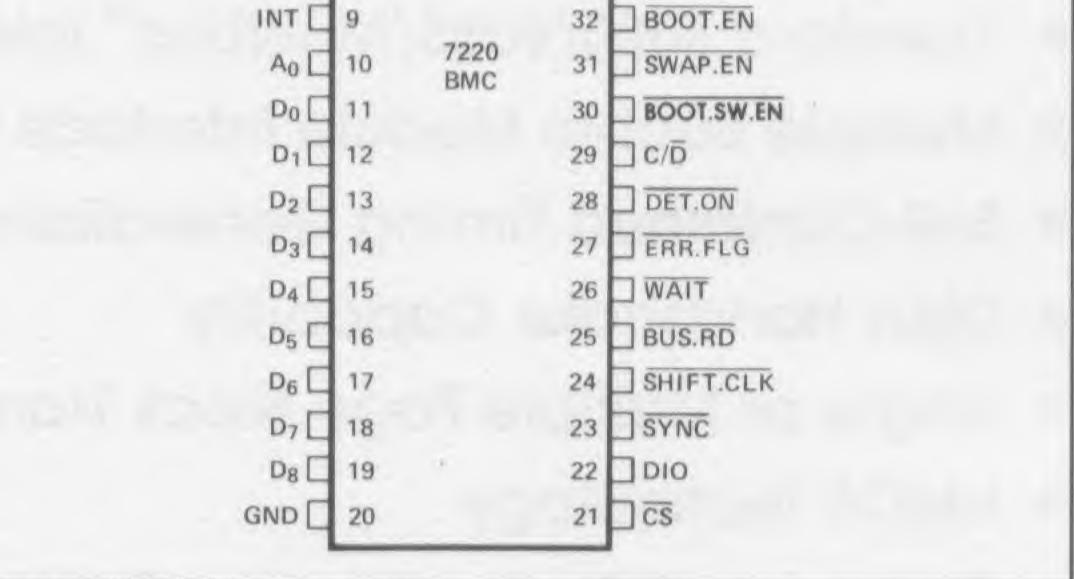

7220

40 🗆 Vcc

39 X+

38 X-

37 Y+

36 TY-

35 TM.A

34 TM.B

33 REP.EN

#### **Pin Description**

#### A<sub>0</sub> (Pin 10)

An address pin used to select one of two internal registers. A logic "0" on this pin shall select the data register and a logic "1" shall select the command/ status register.

#### BOOT.EN (Pin 32)

An active low signal enabling the bootstrap loop replicate function in external circuitry.

#### BOOT.SW.EN (Pin 30)

An active low signal which may be used for enabling the optional BOOT.SWAP of the 7230 CPG.

#### CLK (Pin 3)

The clock shall be a 3.2 to 5 MHz, 50% ±10% duty cycle TTL clock.

#### **CS** (Pin 21)

Chip Select Input. A high on this pin shall disable the device to all but DMA transfers (i.e., it ignores bus activity and goes into a high impedance state).

#### DACK (Pin 7)

DMA acknowledge notifies the BMC that the next memory cycle is available to transfer data. This line should be active only when DMA transfer is desired and the DMA ENABLE bit has been set. CS need not be active during DMA transfers.

#### BUS.RD (Pin 25)

An active low signal that indicates that the DIO line is in the input mode. It shall be used to allow offboard expansion of 7242 FSA devices.

#### C/D (Pin 29)

A high on this line shall indicate that the BMC is beginning command sequence.

#### DET.ON (Pin 28)

8

An active low signal indicating that the magnetic bubble is detecting. It is useful for power saving in the MBM.

### 7220

#### Pin Description (Continued)

#### DIO (Pin 22)

A bidirectional, active high data line that shall be used for serial communications with 7242 FSA devices.

#### DRQ (Pin 8)

A logic high shall indicate that a transfer of data between BMC and host memory is being requested.

#### SHIFT.CLK (Pin 24)

A controller generated clock that initiates data transfer between selected FSA's and their conresponding bubble memory devices. The timing on SHIFT.CLK shall vary depending upon whether data is being read or written to the bubble memory.

#### SWAP.EN (Pin 31)

An active low signal used to create the swap function in external circuits.

#### SYNC (Pin 23)

#### $D_0 - D_8$ (Pins 11 through 19)

A nine bit bidirectional port which can be read or written by utilizing the RD and WR strobes.  $D_0$  shall be the LSB.  $D_8$  shall be a parity signal. When a byte is transferred to the BMC (over  $D_0$ - $D_7$ ), odd parity shall be generated by the BMC and compared to  $D_8$ . When a byte is transferred from the BMC to the host, odd parity over  $D_0$ - $D_7$  shall be generated and transferred as  $D_8$ . Errors in parity shall create an interrupt when enabled by the host CPU.

#### ERR.FLG (Pin 27)

An active low input generated externally by 7242 FSA indicating that an error condition exists.

#### INT (Pin 9)

A logic one shall indicate that the BMC has a new status and requires servicing when enabled by the host CPU.

An active low output utilized to create time division multiplexing slots in a 7242 FSA chain. It shall also indicate the beginning of a data or command transfer between BMC and 7242 FSA.

#### TM.A (Pin 35)

An active low timing signal generated by the decoder logic for determining CUT pulse width.

#### TM.B (Pin 34)

An active low timing signal generated by the decoder logic for determining TRANSFER pulse width.

#### WAIT (Pin 26)

A bidirectional pin that shall be tied to the WAIT pin on other BMC's when operated in parallel. It shall indicate that an error has been detected and that the BMC's should halt until the type of error has been determined. An active low signal.

#### PWR.FAIL (Pin 1)

A logic zero shall indicate that power has failed. It shall force the BMC to begin a controlled stop sequence and hold it in an idle state as RESET does.

#### RD (Pin 5)

Enables BMC to output data to the data bus.

#### REP.EN (Pin 33)

An active low signal used to enable the replicate function in external circuitry.

#### RESET (Pin 4)

A logic zero on this pin shall force the BMC to an idle state and force all bubble memory interface signals to the logic one state (inactive).

#### WR (Pin 6)

9

Enables BMC to receive data from the data bus.

#### X+,X-,Y+,Y- (Pins 39, 38, 37 and 36)

Four active low timing signals generated by the decoding logic and used to create coil drive currents in the bubble memory device.

#### **Functional Description**

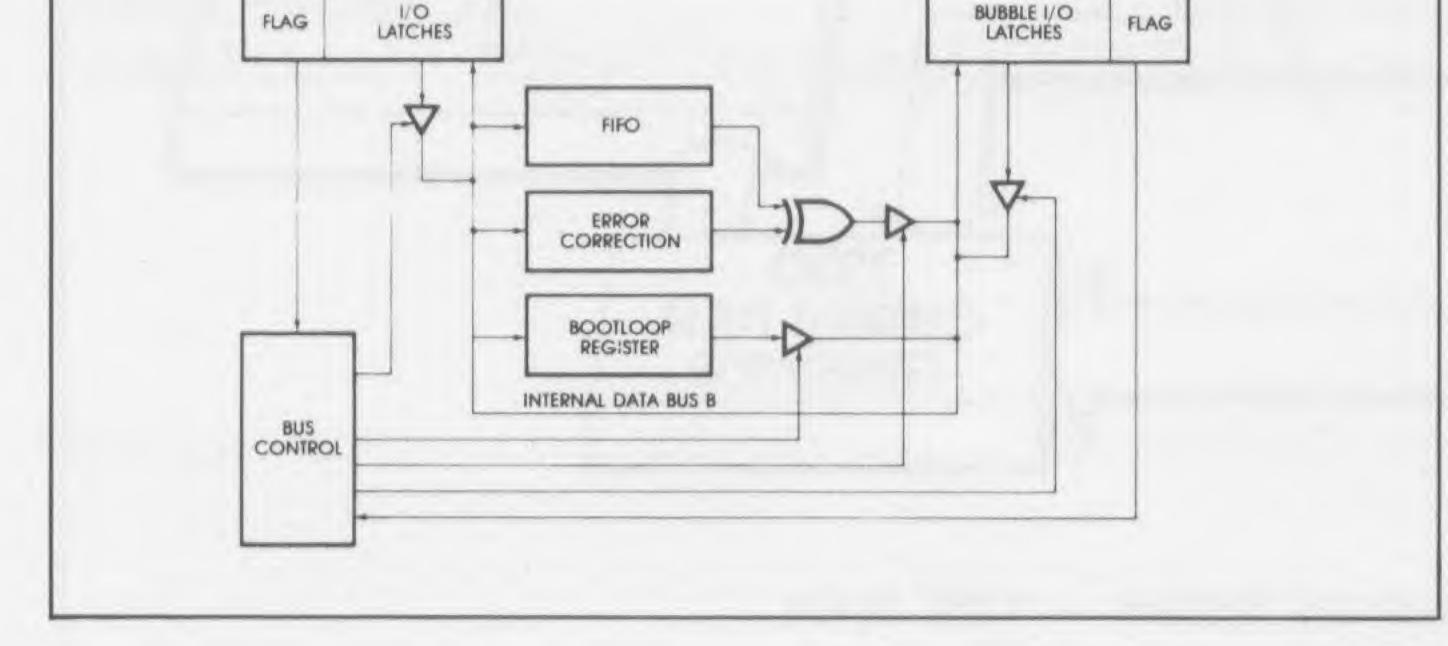

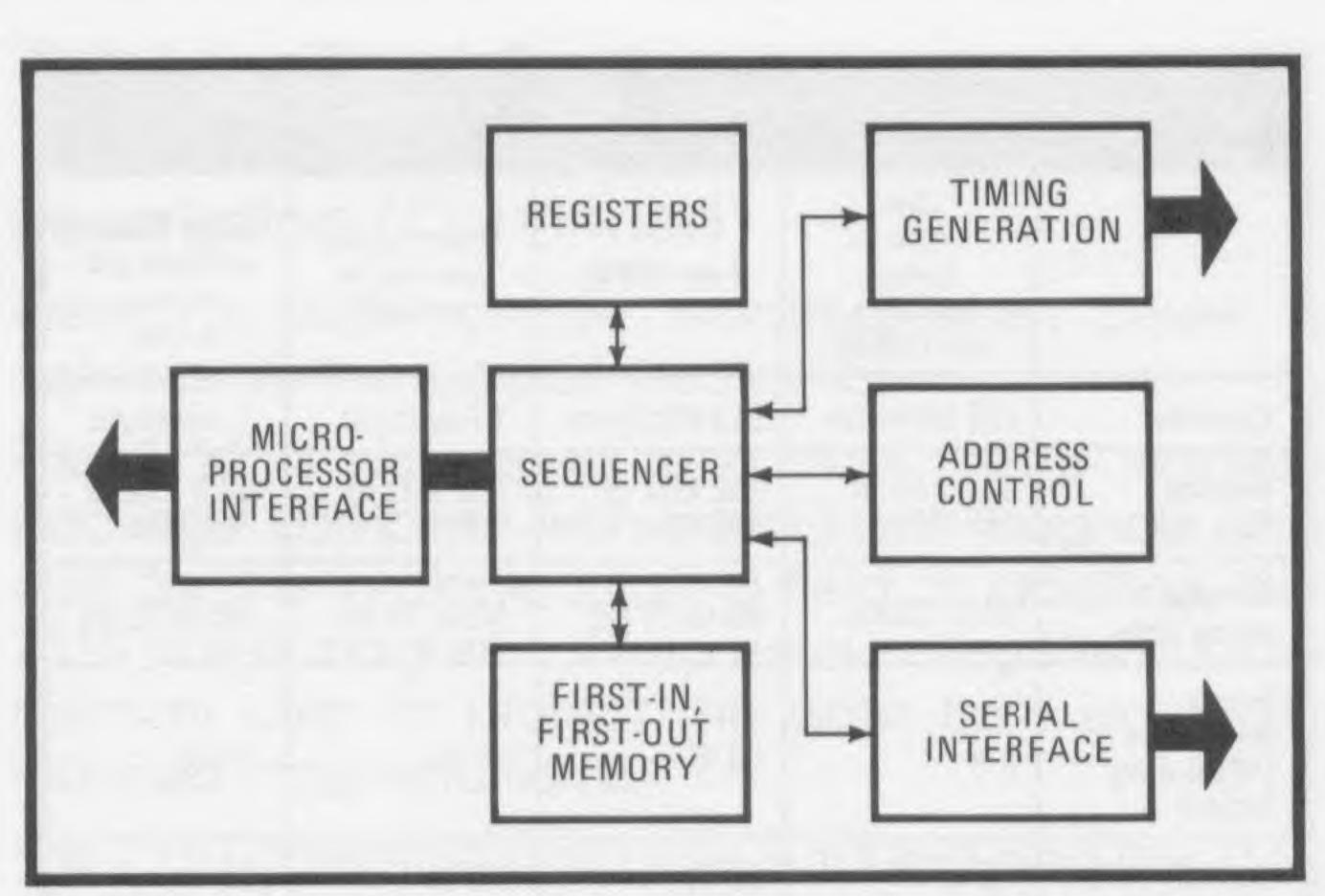

Each block of the 7220 BMC is briefly described as follows:

#### **RESET.OUT (Pin 2)**

An active low signal that disables external logic. It shall be initiated by a PWR.FAIL or RESET signal, but shall not become active until the stopping point in a field rotation is reached (if the BMC is causing the bubble memory drive field to be rotated). System Bus Interface – The System Bus Interface (SBI) logic contains the timing and control logic required to interface the BMC to a non-multiplexed bus. The logic also contains the circuitry to check and generate parity (odd) on transfers across the bus. The interface has input data, output data, and status data latches. The SBI communicates with other BMC sections including parameter registers via the 8-bit internal data bus.

#### Functional Description (Continued)

FIFO - The FIFO is a 40x8 bit FIFO RAM for data storage. The FIFO RAM is dual port so that data may be read (written) at one port while simultaneously being written (read) at the other. It will be the responsibility of the host to make sure there is data/room available in the FIFO for transfers to/from the FSA's. If the host fails to keep up a timing error will result. The FIFO block also contains input and output data latches, providing double data buffering, to improve the R/W cycle times seen at the SBI (minimum 600 nsec cycle time). The FIFO may be used as a general purpose FIFO when a command is not being executed by the BMC Sequencer. In this mode, the FIFO ready status bit will become a FIFO absolutely empty indicator.

available page of data for up to 8 FSA's. The ad dress maintained is the address available for a READ operation. The address for a WRITE operation is calculated by adding a constant to the READ address. The address control logic also contains circuitry to enable multiple page transfers of up to 2048 pages in length.

Register File - The register file contains 7 eight-bit registers that are accessible by the host CPU. Refer to the Register Section for details.

DMA and Interrupt Logic - The BMC DRQ pin has two functions:

(1) If the DMA enable bit in the enable register is set, the DRQ pin, in conjunction with the DACK pin, provides a standard DMA transfer capability, i.e., it has the ability to handshake with an 8257 or 9517 DMA controller chip.

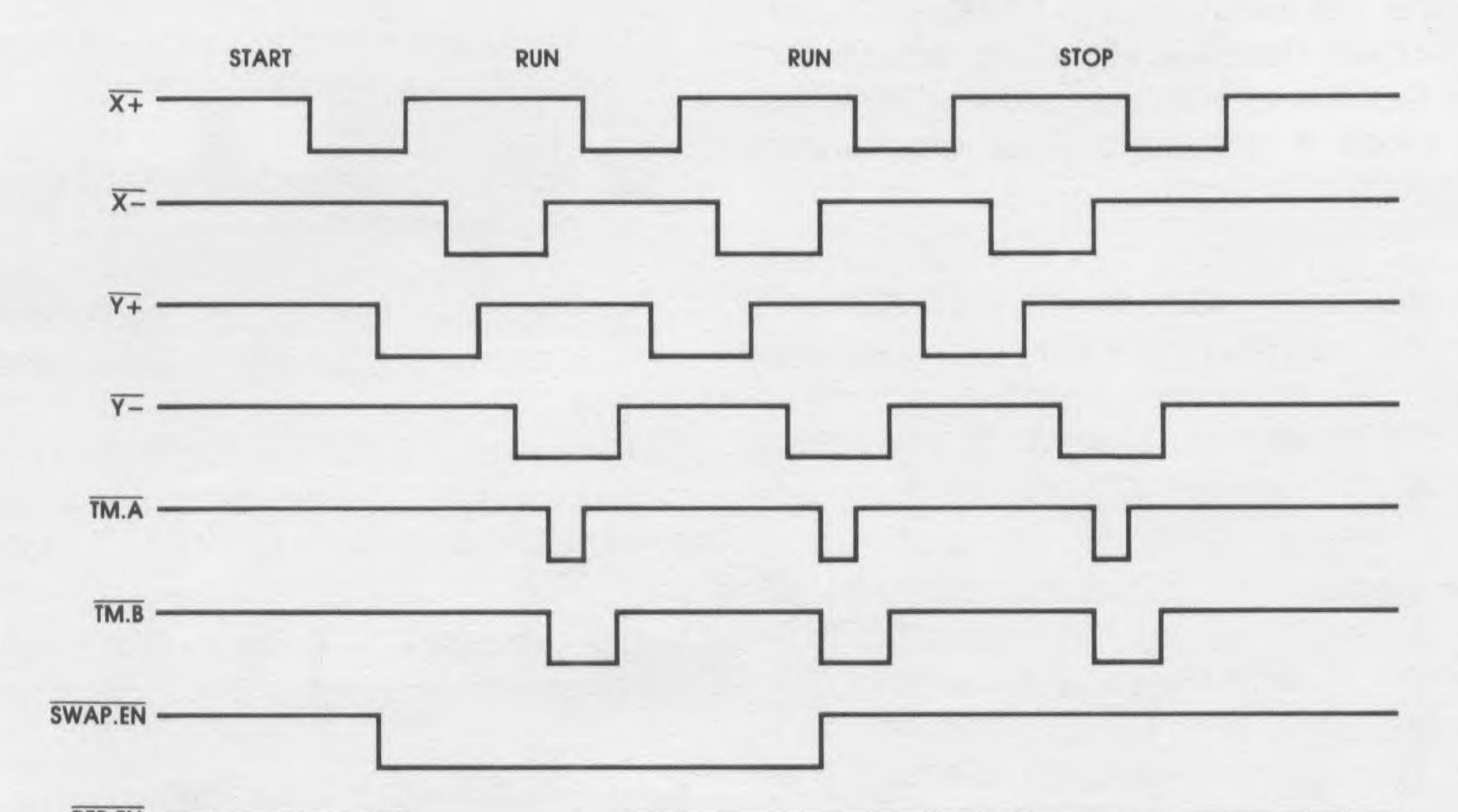

Bubble Signal Decoder - The bubble signal decoder logic contains logic for creating all timing signals for internal use as well as bubble memory timing. The logic consists of counters and decoder circuits. The counter logic consists of three stages. The first stage is a divide-by-four counter that is enabled or disabled by the host CPU. This counter will be used in low frequency systems to provide higher resolution timing. The second stage is a modulo forty counter. The input to this stage can be either the input clock or the output of the modulo four counter. These two counters are used to provide high resolution timing for bubble functions.

The third stage of the counter is a 12 bit counter whose input is the output of the second stage. It is used to count field rotations. It can be preset or cleared by the sequencer. The decoder provides the high speed timing pulses required by the bubble memory and for internal usage. Each signal can be set or reset on any edge of the forty increments of a field rotation (provided by the second stage counter). In addition, some outputs are capable of lasting for more than one field rotation (see Figure 1). Each signal is enabled or disabled by the sesequencer. The outputs of each signal are latched or otherwise designed to be glitch-free.

(2) If the DMA enable bit is reset, the DRQ pin acts as a "ready for data transfer interrupt" pin. It becomes active when 20 bytes may be read from/written into the BMC, it is reset when this condition no longer exists.

This interrupt mode offers an alternative to polling the status word in medium performance systems when DMA is not used.

Bootloop Decoder/Encoder - This block of circuitry does parallel to serial and serial to parallel conversion of data to generate the bidirectional DIO pin, which is the data bus line to FSA's in the Bubble system. It also generates the BUSRD pin which identifies the direction of DIO data transfer if external buffering is required for the DIO line. This block also contains hardware to generate and decode the Bubble Bootstrap loop code during Read and Write Bootloop operations.

FSA Select Logic - This logic determines which FSA's contain the addressed data. Information is obtained from the upper order bits of the block length register and address register (see Register Section). The output information is used by the Bootloop Decoder/Encoder to determine when valid data is available, or should be loaded, on the DIO line.

Sequencer - The BMC contains a microsequencer for control. The sequencer, by decoding the contents of the ROM, interprets commands, sets and resets flags and status bits, and initiates and terminates actions in other parts of the BMC.

MBM Addressing Logic and RAM - The address control logic contains the address of the next

10

Powerfail and Reset - This circuit provides a means of resetting the BMC, and other system hardware via RESET.OUT pin, to a known or start state. PWR.FAIL is monitored by the sequencer on each cycle. When activated, a controller shutdown cycle is started immediately to assure bubble data integrity.

### 7220

#### Registers

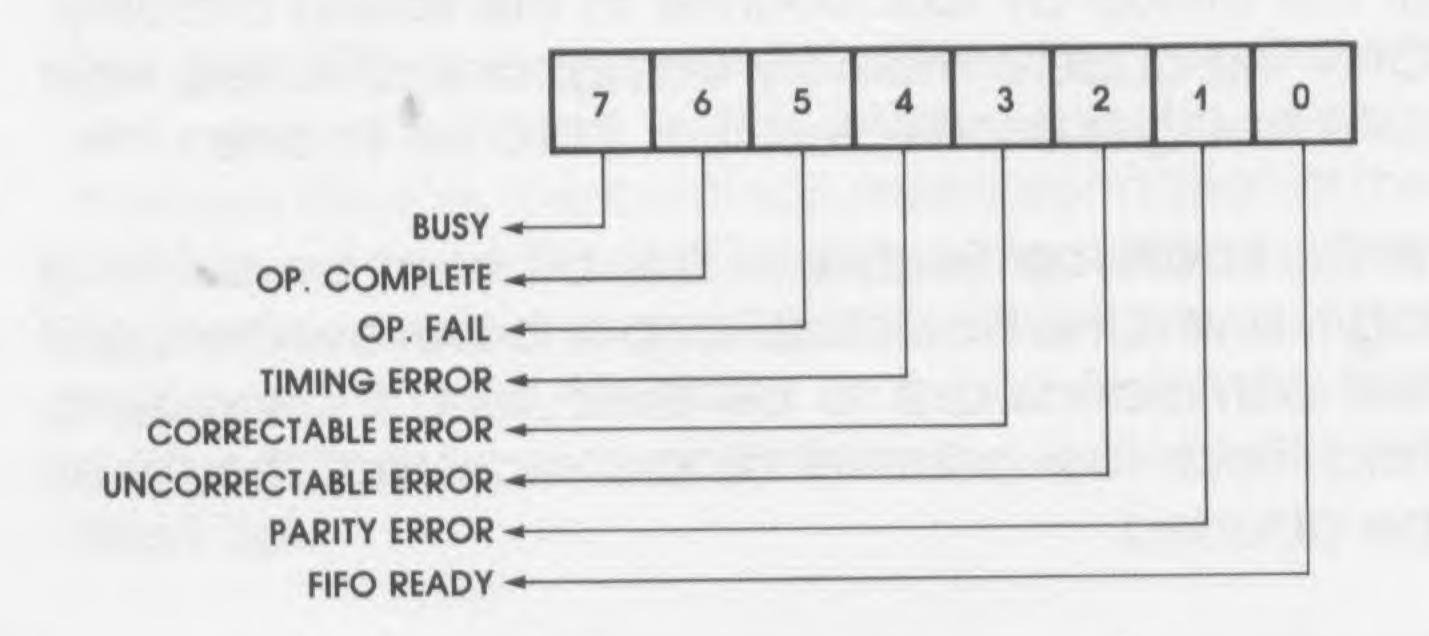

**Directly Addressable Registers** – There are two registers in the BMC that are directly read or written from the data bus. They are a status/command register and a data register. The status/command register is addressed by taking address line A<sub>0</sub> to a logic one and the data register by taking it to a logic zero. The status/command register is actually two separate registers. The status is read when this register is read and the command register can be written by writing into this register. The format of the bits in the status register is:

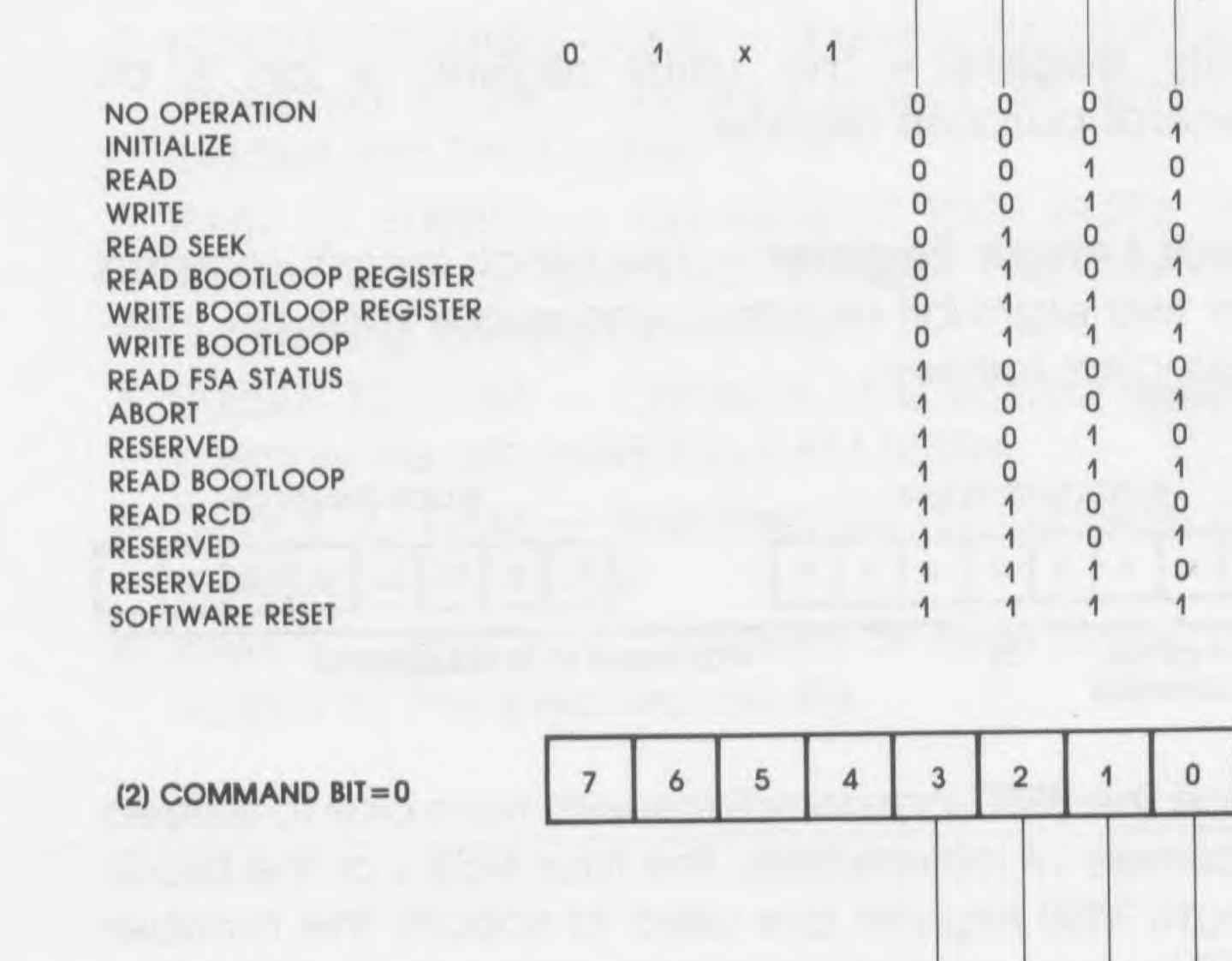

**FIFO READY** – This bit indicates that the FIFO is available to be written or has data ready to be read, when the busy bit is active. It indicates that the FIFO and FIFO input and output registers are all empty when busy is inactive. The Command Register serves a dual purpose. If bit 4 is a logical 1, bits 0–3 will be loaded as a BMC command. If bit 4 is a logical 0, then bits 0–3 will be loaded into the address latch. The four LSB's should be interpreted as follows:

(1) COMMAND BIT = 1

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|---|---|---|---|---|---|---|---|

**BUSY** — This bit indicates that the controller sequencer is still in the process of executing its last command. When the controller is ready to receive a new command the bit is set low.

FIFO

11

**OP COMPLETE** — This bit is set upon successful completion of a command. It is reset whenever the status register is interrogated by the host.

**OP FAIL** — A logic one in this bit indicates that the BMC was unable to successfully complete a command.

**TIMING ERROR** – This bit indicates that an FSA has reported a timing error, or the host has failed to keep up with the BMC and the BMC FIFO has overflowed or gone empty.

**CORRECTABLE ERROR** – Indicates that an FSA has reported a correctable error and shall be reset upon interrogation.

|      | RESERVED                               | 0 | 0 | 0 | 1 |  |

|------|----------------------------------------|---|---|---|---|--|

|      | II | 0 | 0 | 1 | 0 |  |

|      | **                                     | 0 | 0 | 1 | 1 |  |

|      | **                                     | 0 | 1 | 0 | 0 |  |

|      |                                        | 0 | 1 | 0 | 1 |  |

|      | **                                     | 0 | 1 | 1 | 0 |  |

|      |                                        | 0 | 1 | 1 | 1 |  |

|      | **                                     | 1 | 0 | 0 | 0 |  |

|      | COMMAND REG. (READ ONLY)               | 1 | 0 | 0 | 1 |  |

|      | UTILITY REG.                           | 1 | 0 | 1 | 0 |  |

|      | BLOCK LENGTH LSB                       | 1 | 0 | 1 | 1 |  |

| R/W  | BLOCK LENGTH MSB                       | 1 | 1 | 0 | 0 |  |

| R/ W | ENABLE (WRITE ONLY                     | 1 | 1 | 0 | 1 |  |

|      | ADDRESS LSB                            | 1 | 1 | 1 | 0 |  |

|      | ADDRESS MSB                            | 1 | 1 | 1 | 1 |  |

**Data Register** — The source or destination of data read from or written to the data register is specified by first writing to the status/command register with bit 4=0 and bits 0-3 set corresponding to the desired register. The data then may be transferred by addressing the data register. For example, to read the ADDRESS LSB register of the BMC, the CPU must first write the bit pattern XXX01110 to the status/

**UNCORRECTABLE ERROR** – Indicates that the last data block transferred contained an uncorrectable error. It shall be reset upon interrogation.

**PARITY ERROR** – Indicates a parity check failure and shall be reset upon interrogation.

command register.

The CPU may then read the ADDRESS by addressing the data register (Pin A0=0) and performing a read operation. If the FIFO is selected as source or destination, then sequential FIFO locations shall be accessed with sequential reads or writes (only one status/command operation required). Otherwise, sequential registers are accessed with sequential

#### **Registers (Continued)**

reads or writes (e.g., COMMAND REG, BLOCK LENGTH LSB, etc.). Again, only one status/command operation is required.

FIFO Register — Data read or written into the FIFO is valid only when the FIFORDY bit is true in the status/ command register.

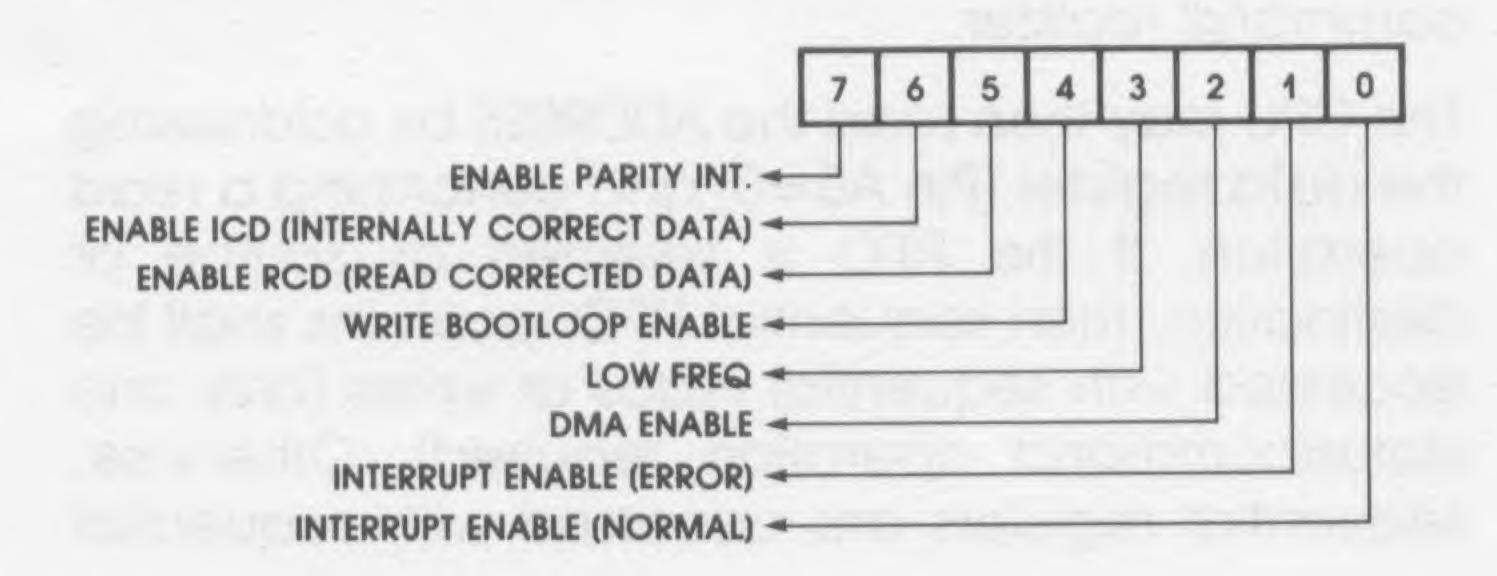

Interrupt Enable (Normal) – A logic one shall enable the BMC to interrupt the CPU upon completion of a task with the INT pin.

**Interrupt Enable (Error)** – A logic one shall permit the BMC to interrupt the CPU upon detection of an error condition, independent of its correctability, via the INT pin.

**DMA Enable** — A logic one shall cause the BMC to request data transfers via DRQ and DACK signals. A logic zero shall cause all transfers to occur via polling the status register or using DRQ as an interrupt pin. Refer to functional description for DMA and Interrupt Logic.

Utility Register – The utility register is an 8 bit general purpose register.

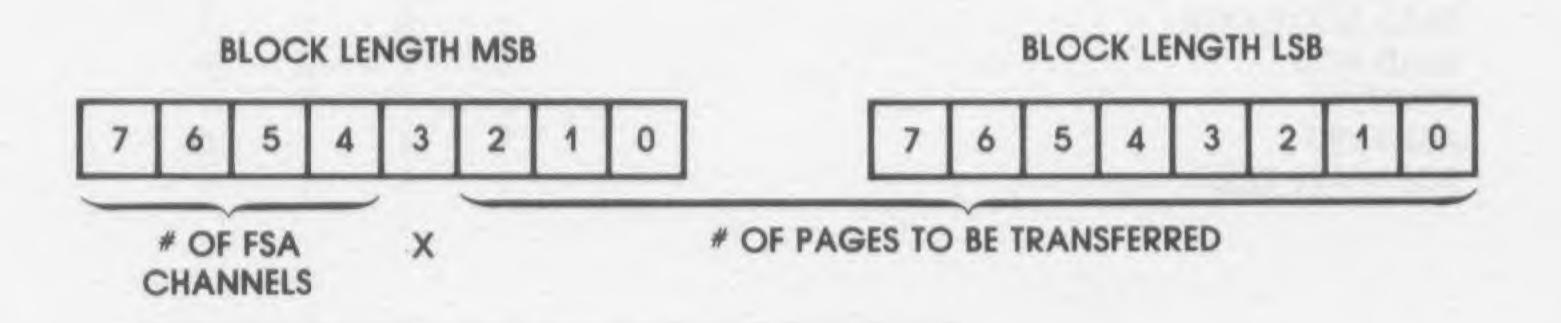

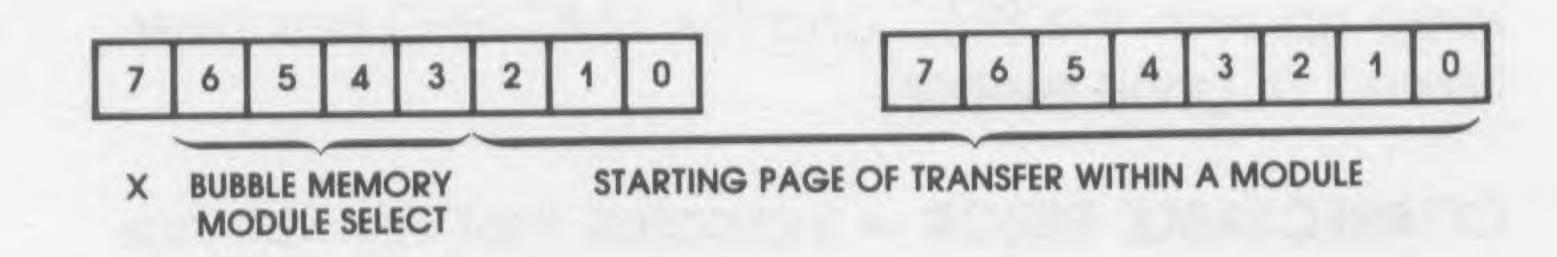

Block Length Register — The block length registers are two eight-bit registers whose bits shall be interpreted as follows:

Since the BMC can interface with from one to sixteen channels of information, the four MSB's of the block length MSB register are used to specify the number of FSA channels to be used in each transfer. The four MSB's shall be interpreted as follows: Low Freq — This bit shall be set to enable operation of the divide by four counter in the timing circuitry. Only the bubble memory timings are affected; host CPU timing is unaffected. For 7110 set to one.

Write Bootloop Enable – This bit must be set to a logic one if the bootstrap loop is to be rewritten, or if test commands are to be executed. If it is a zero, and these four commands are received, they shall be aborted.

**Enable RCD** – Enables the BMC to attempt to correct the data as it is passed to the BMC. In the event of an uncorrectable error bad data may be passed

| One FSA       | 0 | 0 | 0 | 0 |  |

|---------------|---|---|---|---|--|

| Two FSA's     | 0 | 0 | 0 | 1 |  |

| Four FSA's    | 0 | 0 | 1 | 1 |  |

| Eight FSA's   | 0 | 1 | 1 | 1 |  |

| Sixteen FSA's | 1 | 1 | 1 | 1 |  |

|               |   |   |   |   |  |

7654

12

These four bits, in conjunction with the address bits, determine which memory modules are being accessed for a given transfer.

**Enable Register** – The enable register contains flags set by the host that will enable or disable various functions within the BMC or FSA. The bits in the register are interpreted as follows:

to the host.

**Enable ICD** – Enables the BMC to attempt correction of data errors before transferring the data containing the error into host memory.

**Enable Parity Interrupt** — Enables the BMC to interrupt the host CPU upon detection of a parity error on the data bus.

Address Registers — The address registers consist of two eight bit registers whose bits are interpreted as follows:

The eleven LSB's designate the starting page address of the data transfer, regardless of the number of memory modules being accessed. The four MSB's, along with the four MSB's of the block length register determine which modules are to be accessed. Table 1 designates the FSA's that are to be used with various combinations of address and block length MSB's.

### 7220

### Table 1FSA Channels Selected vs Address Bits

| Block Length MSB | 0000 | 0001   | 0011           | 0111    | 1111 |

|------------------|------|--------|----------------|---------|------|

| Address MSB      |      |        |                |         |      |

| 0000             | 0    | 0, 1   | 0, 1, 2, 3     | 0 to 7  | ALL  |

| 0001             | 1    | 2,3    | 4, 5, 6, 7     | 8 to 15 |      |

| 0010             | 2    | 4,5    | 8, 9, 10, 11   | -       |      |

| 0011             | 3    | 6,7    | 12, 13, 14, 15 |         |      |

| 0100             | 4    | 8,9    | _              | _       |      |

| 0101             | 5    | 10, 11 |                | -       |      |

| 0110             | 6    | 12, 13 | _              | _       |      |

| 0111             | 7    | 14, 15 | _              |         |      |

| 1000             | 8    | _      | _              |         |      |

| 1001             | 9    | -      | _              |         |      |

| 1010             | 10   | -      | _              | -       |      |

| 1011             | 11   |        | -              | -       |      |

| 1100             | 12   | -      | -              | _       |      |

| 1101             | 13   | -      | _              | _       |      |

| 1110             | 14   | -      | -              | _       |      |

| 1 1 1 1          | 15   | -      |                |         |      |

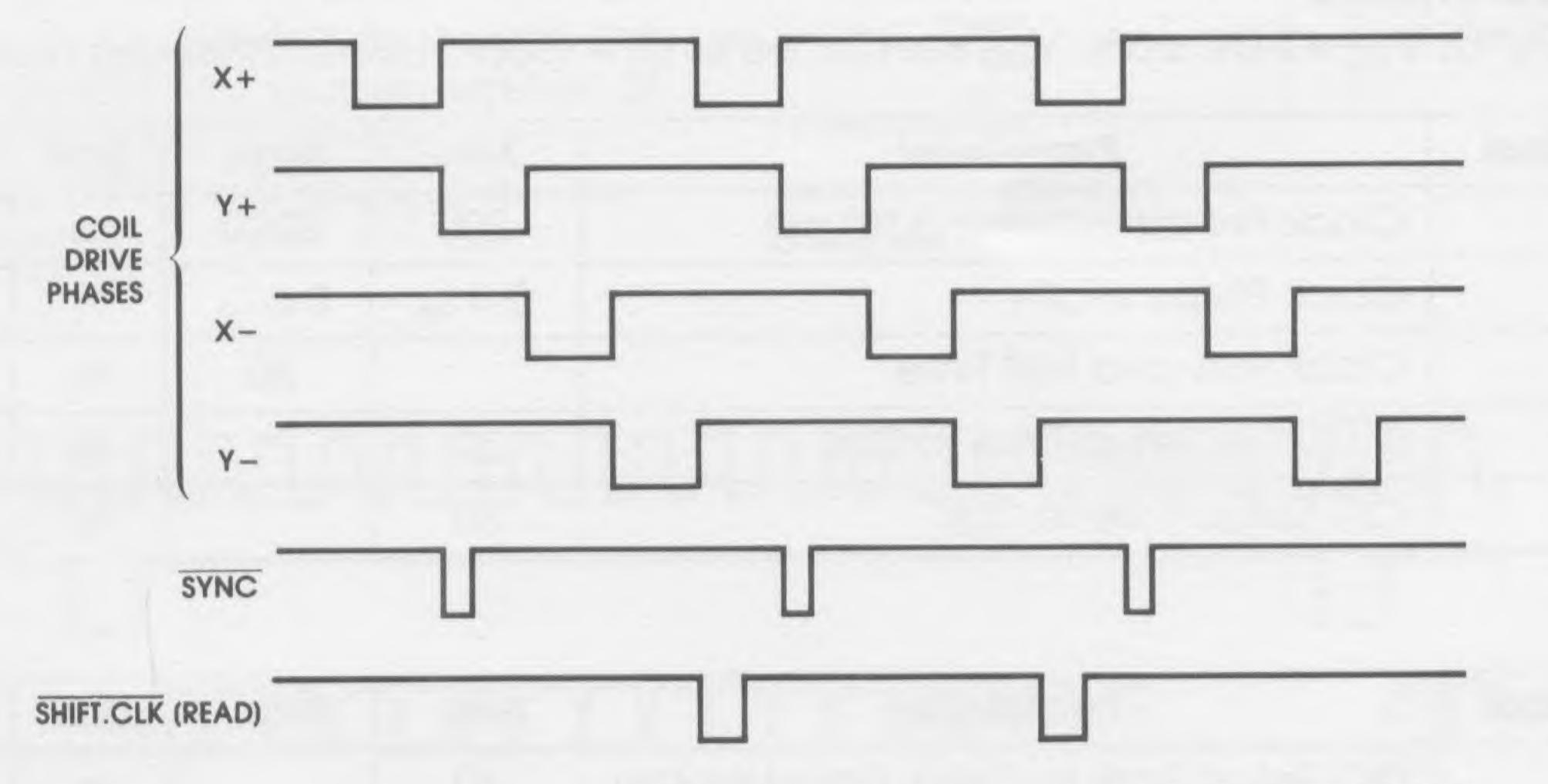

#### Figure 1. Typical Bubble Timing Signals

13

#### Commands

When a command is sent the BMC will be busy executing that command until 1) it is completed, 2) a fatal error occurs, or 3) an ABORT command is sent. The commands are briefly described as follows:

No-Operation - Causes the BMC to enter an idle state.

**Read FSA Status** – Causes the BMC to interrogate the status of all FSA's and store in the BMC FIFO. Note that the entire status of all FSA's can be read and stored in the first 16 bytes of the BMC FIFO with one command. The host CPU shall then have access to FSA status.

**Software Reset –** Resets all registers and the FIFO except initialization parameters.

Abort - Terminates present BMC activity.

Initialize – Causes the BMC to read the contents of the bootstrap loop on each bubble device and store the contents in the associated FSA bootstrap loop register. The memory devices shall be stopped at a known address to be consistently defined as page address zero.

**Read** – Causes data to be transferred from bubble memory to BMC FIFO. Data is transferred from each bubble device selected per Table 1.

Write – Causes data to be transferred from BMC FIFO to bubble memory. Again, data is transferred to each bubble device per Table 1.

Seek - Causes the BMC to rotate the selected bub-

**Read Bootloop** – Causes the BMC to read the selected bubble device bootstrap loop, decode, and store the results in the FIFO.

**Read RCD** – Commands Formatter to output corrected data which is in FSA's FIFO.

#### Interfaces

14

**CPU Interface** – The BMC can interface asynchronously to the host CPU. With a 5 MHz clock, it is capable of sustaining a 1.6 Mbyte/sec transfer rate, while data/room is available in the BMC FIFO.

Software Interface – The general procedure for communicating with the BMC is:

ble device to the address specified and stop (no data transfers occur). The BMC stops the devices in such a manner that the selected address will be the first available block if a read to that address is specified.

**Read Bootloop Register** – Causes the BMC to read the contents of the selected FSA's bootloop register and store in FIFO. The data shall then be available to the host CPU. If more than one FSA is selected, bootloop register data will be interleaved.

Write Bootloop Register – Causes the contents of the BMC FIFO to be written into the selected FSA bootloop register. Twenty bytes are needed for each FSA selected since only 160 bits are required per FSA. Again, if more than one FSA is selected, the host must interleave the data properly.

- (1) Read the status/command register until BMC is not busy.

- (2) Pass parameters to the BMC by addressing the proper register.

- (3) Examine the status register to determine whether the operation was successful.

Commands, status, and parameters shall be passed via I/O commands. Data can be passed either I/O commands or via a DMA channel.

Serial Interface – Refer to 7242 FSA Specification for a description of the BMC/FSA interface.

Bubble Interface - The BMC/bubble memory inter-

Write Bootloop – Enables the host CPU to replace the existing contents of a bubble device bootloop with data stored in the BMC FIFO. Encoding is done in hardware so only 40 bytes of data are required. As a precaution, this command shall also require an enable bit be set in the enable register. face consists of 10 active low timing signals. The starting and stopping point of each signal is determined by the decoder logic and is mask programmable. Each signal may occur every field rotation or only once in a number of field rotations. The field rotation in which a timing pulse occurs is controlled by the sequence logic. Figure 1 illustrates typical timing signals.

# intel magnetics.

## 7230 CURRENT PULSE GENERATOR FOR BUBBLE MEMORIES

#### Features

Ideal for Use with IM's Bubble Memories

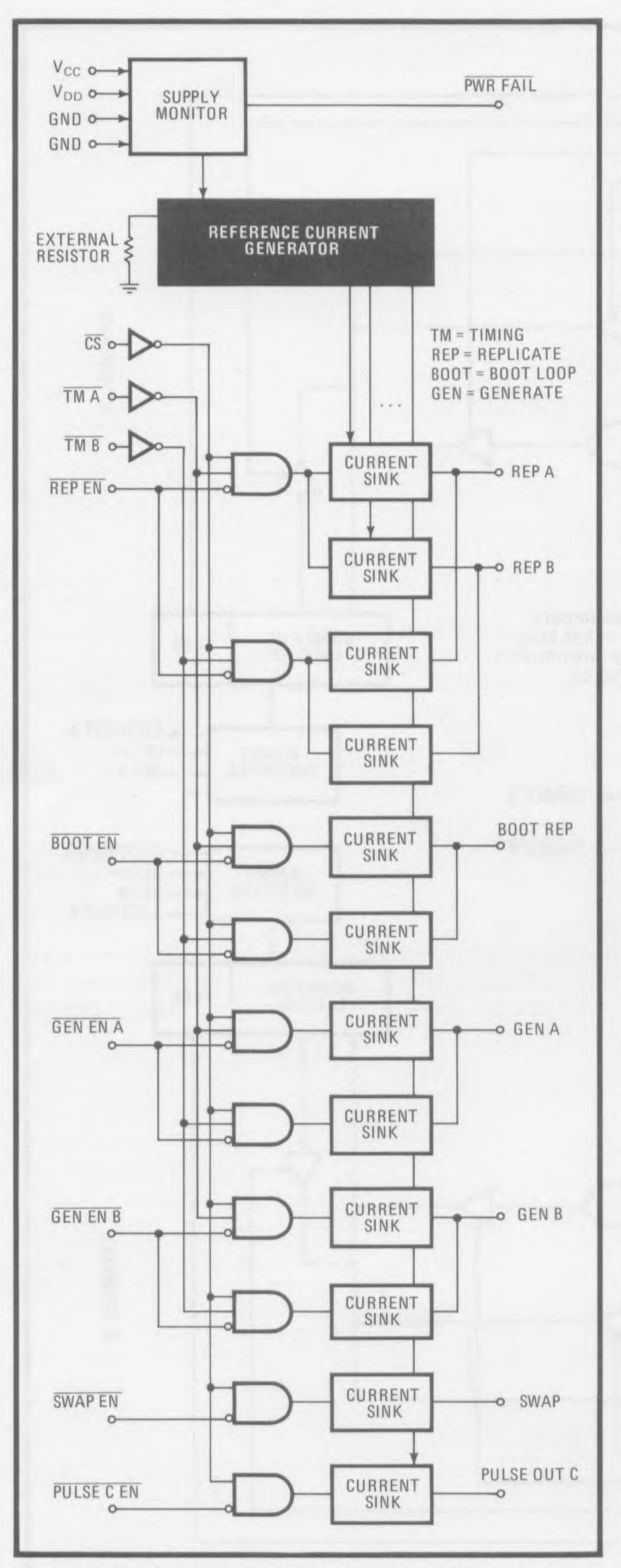

#### Description

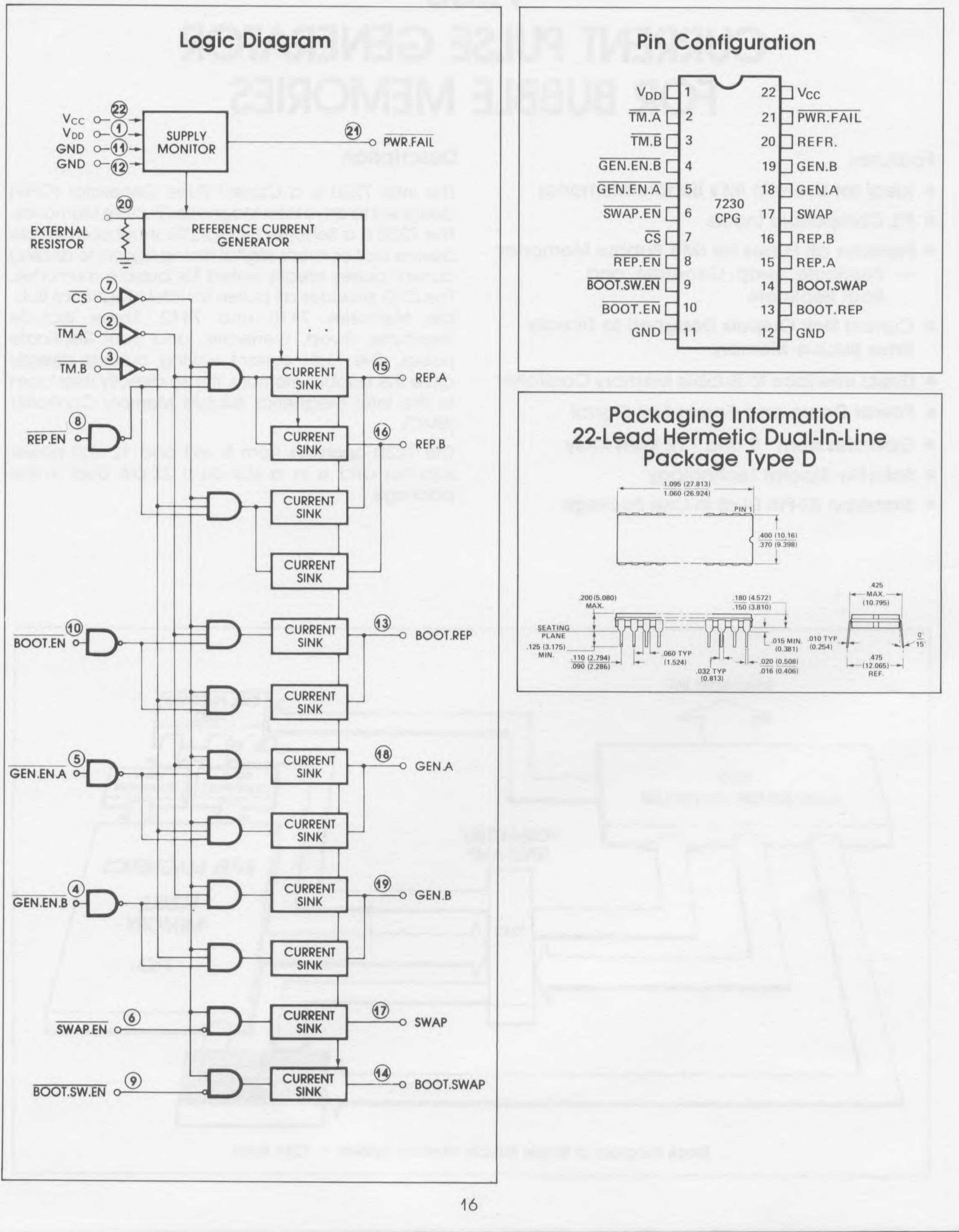

The Intel 7230 is a Current Pulse Generator (CPG) designed to drive Intel Magnetics Bubble Memories. The 7230 is a Schottky Bipolar, TTL input compatible device that converts digital timing signals to analog current pulses ideally suited for bubble memories. The CPG provides all pulses for Intel Magnetics Bubble Memories 7110 and 7112. These include Replicate, Swap, Generate, and Boot Replicate pulses. The high current sinking outputs directly drive the bubble memory. It also directly interfaces to the Intel Magnetics Bubble Memory Controller (BMC).

- TTL Compatible Inputs

- Provides all Pulses for IM's Bubble Memories

- Replicate, Swap, Generate, and Boot Replicate

- Current Sink Outputs Designed to Directly Drive Bubble Memory

- Direct Interface to Bubble Memory Controller

- Power Down and Power Fail Signal

- Operates from +5 and +12 Volts Only

- Schottky Bipolar Technology

- Standard 22-Pin Dual In-Line Package

The 7230 operates from 5 volt and 12 volt power supplies and is in a standard 22-pin dual in-line package.

7230

## 7230

#### **Pin Description**

#### BOOT.EN (Pin 10)

An active low input enabling the BOOT.REP output current pulse.

#### BOOT.REP (PIN 13)

An output providing the current pulse for bootstrap loop replication in the bubble memory.

#### BOOT.SWAP (Pin 14)

#### PWR.FAIL (Pin 21)

An active low output indicating that either  $V_{CC}$  o  $V_{DD}$  is less than 80% of its nominal value.

#### REFR. (Pin 20)

The pin for the reference current generator to which an external resistance must be connected.

#### **REP.A (Pin 15)**

An output providing the current pulse for replication of data in the "A" quads of the bubble memory.

#### **REP.B** (Pin 16)

An optional output providing a current pulse which may be used for writing data into the bootstrap loop.

#### BOOT.SW.EN (Pin 9)

An active low input enabling the BOOT.SWAP output current pulse.

#### CS (Pin 7)

An active low input for selecting the chip. The chip powers down during deselect.

#### **GEN.A (Pin 18)**

An output providing the current pulse for writing data into the "A" quads of the bubble memory.

#### GEN.B (Pin 19)

An output providing the current pulse for writing data into the "B" quads of the bubble memory.

#### CF.D (FIII 10)

An output providing the current pulse for replication of data in the "B" quads of the bubble memory.

#### REP.EN (Pin 8)

An active low input enabling the REP.A and REP.B outputs.

#### SWAP (Pin 17)

An output providing the current pulse for exchanging the data between the input track and the storage loops in the bubble memory.

#### SWAP.EN (Pin 6)

An active low input enabling the SWAP output.

#### TM.A (Pin 2)

An active low timing signal determining the cut pulse widths of the BOOT.REP, GEN.A, GEN.B, REP.A and REP.B outputs.

#### GEN.EN.A (Pin 5)

An active low input enabling the GEN.A output current pulse.

#### GEN.EN.B (Pin 4)

An active low input enabling the GEN.B output current pulse.

#### TM.B (Pin 3)

An active low timing signal determining the transfer pulse widths of the BOOT.REP, GEN.A, GEN.B, REP.A and REP.B outputs.

17

## 7230

## **D.C. and Operating Characteristics** $T_A = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = 5.0V \pm 5\%$ , $V_{DD} = 12V \pm 5\%$ , unless otherwise specified.

| Cumphral |                                          | 2    | Limits |       |      | Test Conditions            |

|----------|------------------------------------------|------|--------|-------|------|----------------------------|

| Symbol   | Parameter                                | Min. | Typ.   | Max.  | Unit | Test Conditions            |

| IIL      | Input Low Current                        |      |        | -0.4  | mA   | $V_{IL} = 0.4V$            |

| IIH      | Input High Current                       |      |        | 20    | μΑ   | $V_{\rm H}=2.7V$           |

| VIL      | Input Low Voltage                        |      |        | 0.8   | V    |                            |

| VIH      | Input High Voltage                       | 2.0  |        |       | V    |                            |

| Vc       | Input Clamp Voltage                      |      |        | -1.5  | V    | = -18  mA                  |

| ICEX     | Output Leakage Current                   |      |        | 1.0   | mA   |                            |

| VOL      | PWR.FAIL Output Low Voltage              |      |        | 0.4   | V    | $I_{OL} = 4 \text{ mA}$    |

| VOH      | PWR.FAIL Output High Voltage             | 2.5  |        |       | V    | $I_{OH} = -0.4 \text{ mA}$ |

| los      | PWR.FAIL Output Short<br>Circuit Current | -20  |        | - 100 | mA   | $V_{CC} = 5.5V$            |

| ICC1     | Current from V <sub>CC</sub> —selected   |      |        | 32    | mA   | $\overline{CS} = V_{IL}$   |

| IDD1     | Current from V <sub>DD</sub> —selected   |      |        | 40    | mA   | $\overline{CS} = V_{IL}$   |

| IDD2     | Current from V <sub>DD</sub> -power down |      | -      | 6     | mA   | $\overline{CS} = V_{IH}$   |

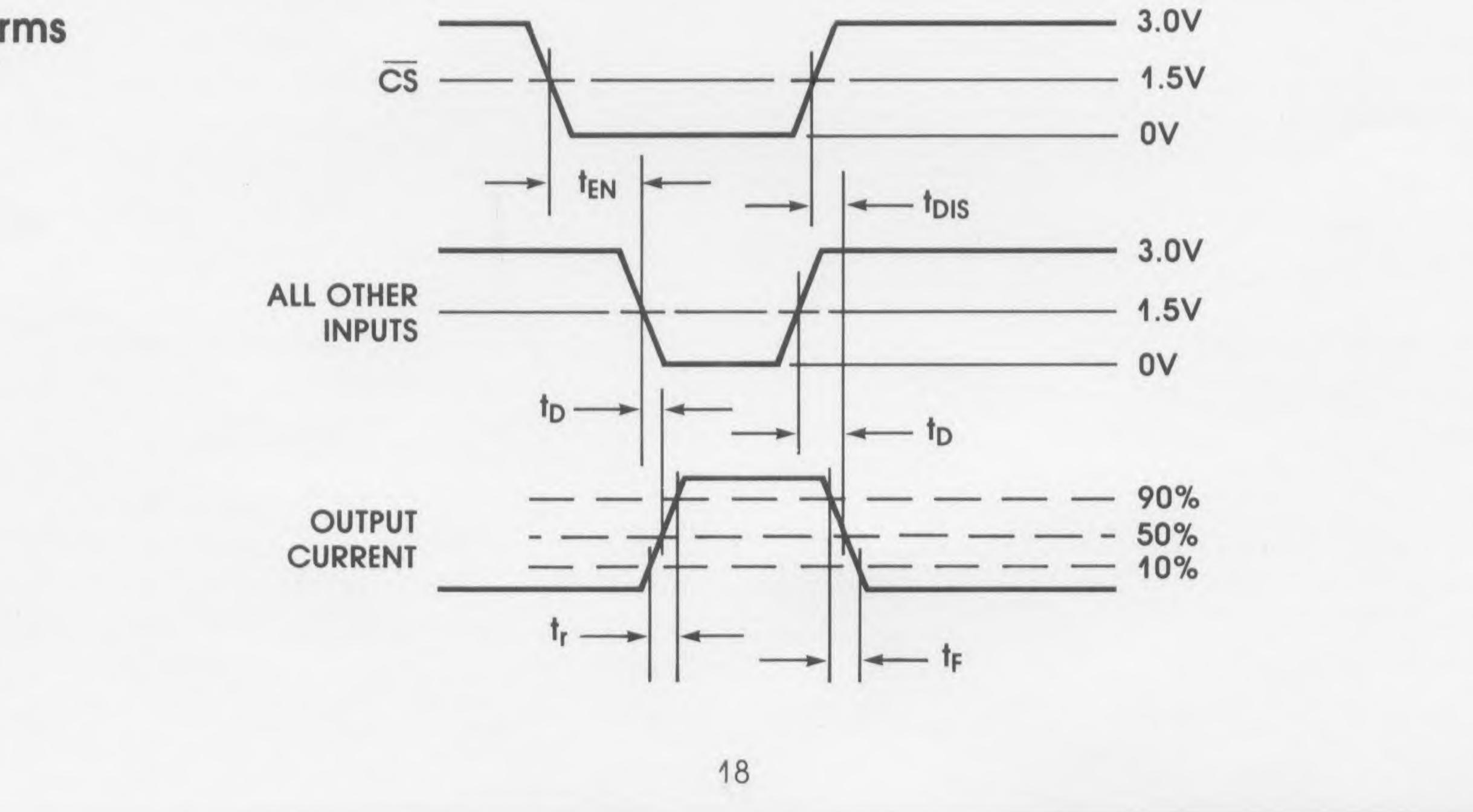

#### A.C. Characteristics $T_A = 0^{\circ}C \text{ to } +70^{\circ}C, V_{CC} = 5.0V \pm 5\%, V_{DD} = 12V \pm 5\%$

| Symbol          | Parameter                | Min. | Max. | Unit | <b>Test Conditions</b> |

|-----------------|--------------------------|------|------|------|------------------------|

| t <sub>D</sub>  | Propagation Delay        |      | 50   | ns   |                        |

| t <sub>r</sub>  | Output Current Rise Time |      | 40   | ns   |                        |

| † <sub>F</sub>  | Output Current Fall Time |      | 40   | ns   |                        |

| tDIS            | CS Disable Time          |      | 50   | ns   |                        |

| t <sub>EN</sub> | CS Enable Time           |      | TBD  | μS   |                        |

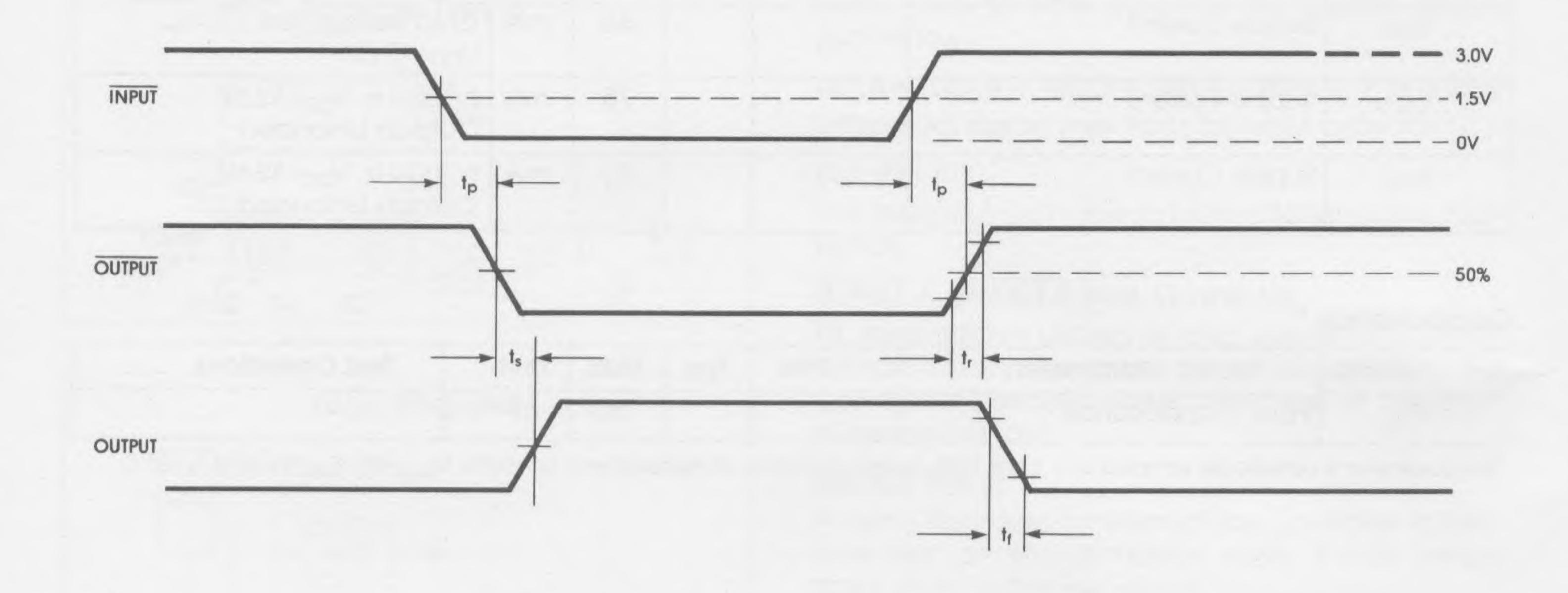

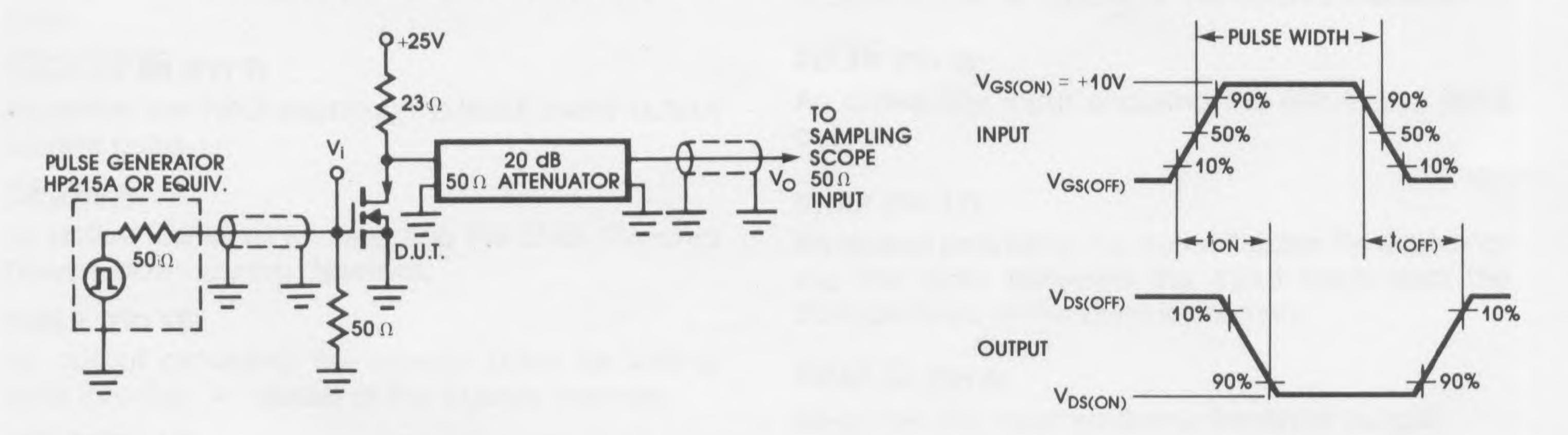

Waveforms

## 7230

#### Capacitance\* $T_A = 25 °C$

| Symbol | Test              | Typ. | Max. | Unit | Test Conditions |

|--------|-------------------|------|------|------|-----------------|

| CIN    | Input Capacitance |      | 10   | pF   |                 |

\*This parameter is periodically sampled and not 100% tested. Condition of measurement is f=IMHz, V<sub>bias</sub>=2V.

#### **Output Currents**

|                             | N            | ominal Values at 50 | Nominal Values at 50 KHz |  |  |  |  |  |  |

|-----------------------------|--------------|---------------------|--------------------------|--|--|--|--|--|--|

| Output ( $V_{OUT} = 3.0V$ ) | Current (mA) | Pulse Width (µs)    | Duty Cycle (%)           |  |  |  |  |  |  |

| REP.A, REP.B CUT            | 180          | 0.25                | 0.006                    |  |  |  |  |  |  |

| REP.A, REP.B TRANSFER       | 140          | 5.0                 | 0.12                     |  |  |  |  |  |  |

| BOOT.REP CUT                | TBD          | 0.25                | 1.3                      |  |  |  |  |  |  |

| BOOT.REP TRANSFER           | TBD          | 0.25                | 1.3                      |  |  |  |  |  |  |

| GEN.A, GEN.B CUT            | 130          | 0.25                | 1.3                      |  |  |  |  |  |  |

| GEN.A, GEN.B TRANSFER       | 40           | 3.0                 | 15                       |  |  |  |  |  |  |

| SWAP                        | 140          | 30.0                | 0.8                      |  |  |  |  |  |  |

| BOOT.SWAP                   | TBD          | *See Note           |                          |  |  |  |  |  |  |

Two-level pulses are defined as shown:

19

Note: Writing data into the bootstrap loop would require 4096 pulses of 20 µs width.

\*COMMENT: Stresses above those listed under "Ab-

#### **Absolute Maximum Ratings\***

Temperature Under Bias.....-20°C to +80°C Storage Temperature .... -65°C to +150°C Vcc and Input Voltages.....-0.5V to +7V V<sub>DD</sub> and Output Voltages.....-0.5V to +14V

solute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

.

# intel magnetics.

## 7242 **DUAL FORMATTER/SENSE AMPLIFIER** FOR BUBBLE MEMORIES

#### Features

Description

- Ideal for Use with IM's Bubble Memories

- Dual Channel

- On-Chip Sense Amplifiers

- Automatically Handles Redundant Loops

- Error Detection/Correction done Automatically

- FIFO Data Block Buffer

- Daisy-Chained Selects for Multiple Bubble Memory Systems

- MOS N-Channel Technology

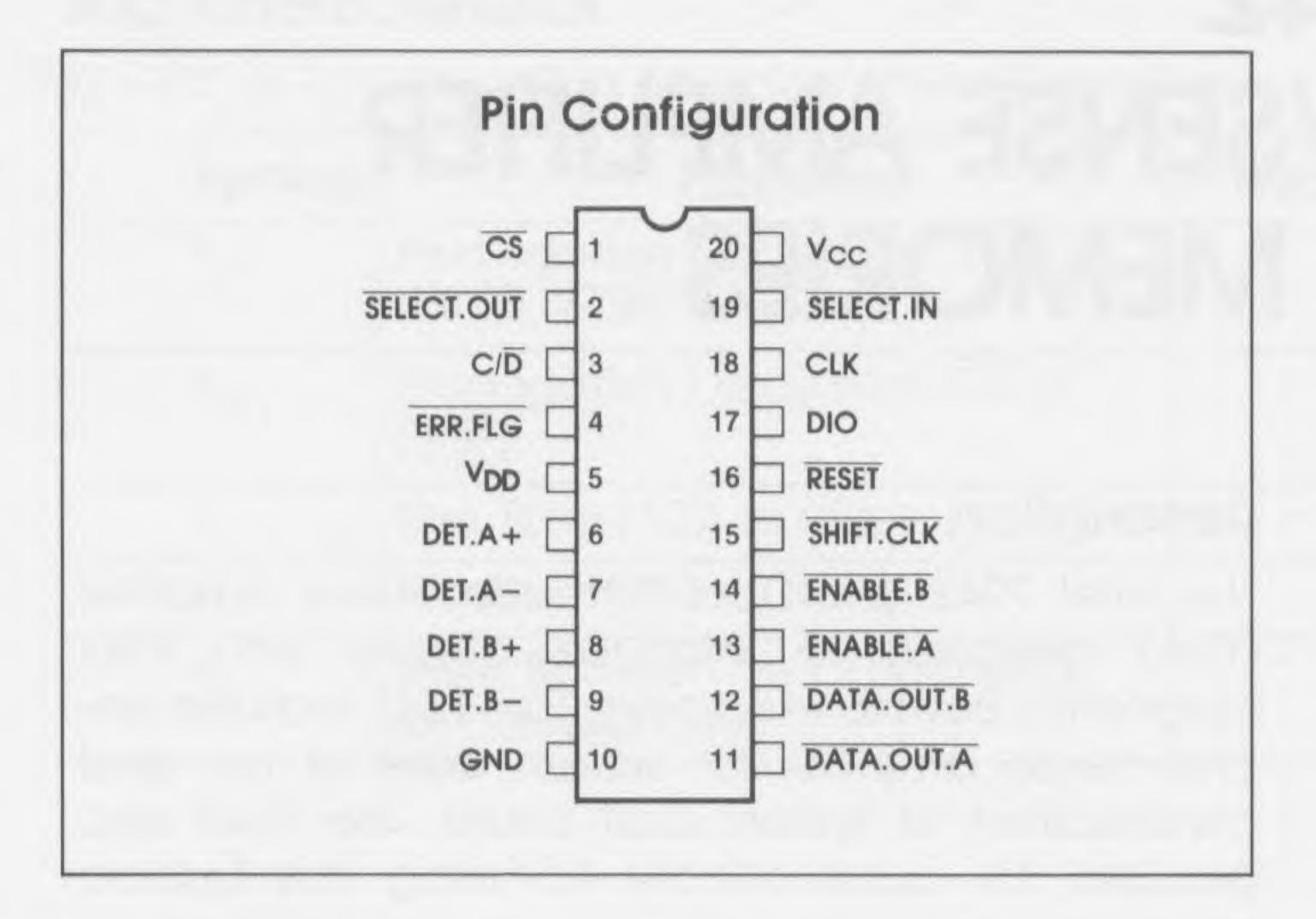

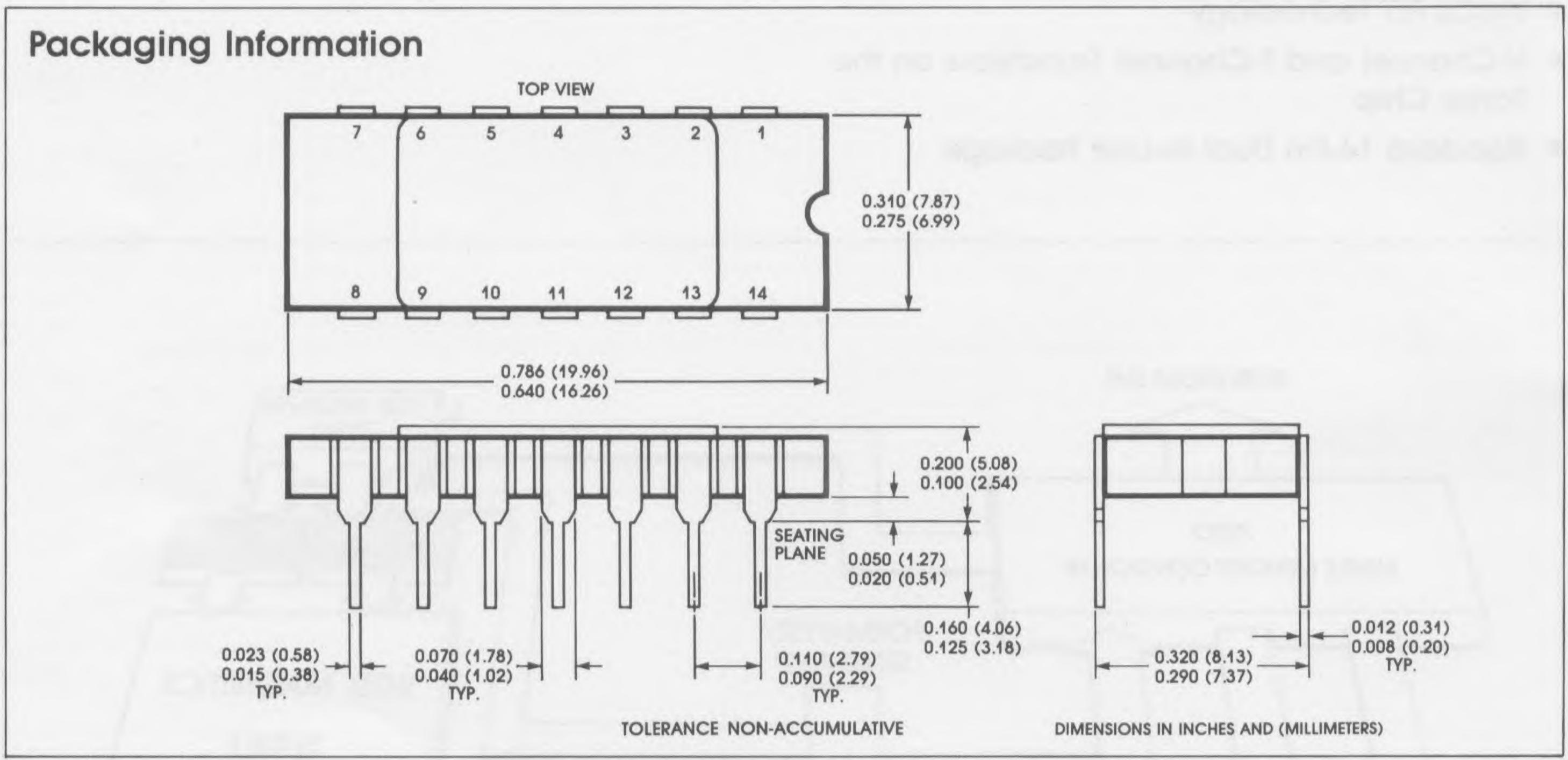

- Standard 20-Pin Dual In-Line Package

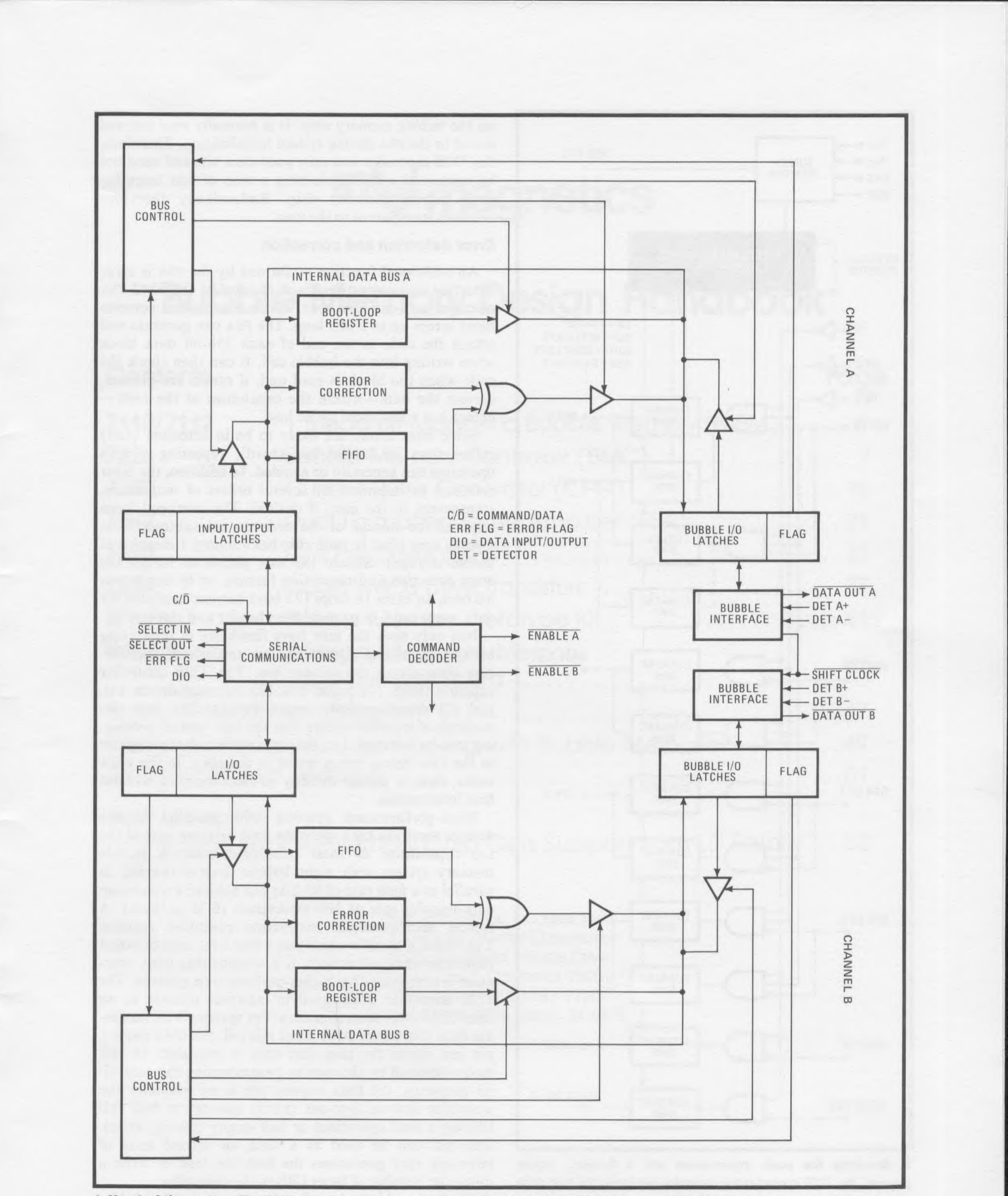

The Intel 7242 is a Dual Formatter/Sense Amplifier (FSA) designed to interface directly with Intel Magnetics Bubble Memories. The 7242 features onchip sense amplifier for system ease of use and minimization of system part count. The 7242 also provides for automatically handling the bubble memories' redundant loops so they appear transparent to the user. In addition, complete burst error detection and correction can be done automatically by this device.

The 7242 has a full FIFO data block buffer. This device can be daisy-chained for multiple bubble memory systems. Up to eight FSA can be controlled by one 7220 Bubble Memory Controller (BMC).

The 7242 utilizes an advanced NMOS technology to incorporate the on-chip sense amplifiers and other unique features. The device is packaged in a standard high density 20-pin dual in-line package.

### 7242

#### **Pin Description**

#### C/D (Pin 3)

Command/Data signal. This signal shall cause the FSA to enter a receive command mode when high and to interpret the serial data line as data when low. Any previously active command will be immediately terminated by  $C/\overline{D}$ .

#### CLK (Pin 18)

A 0.5 to 5 MHz, 50%  $\pm$  10% duty cycle TTL level clock used to generate internal timing.

#### CS (Pin 1)

An active low signal used for multiplexing of FSA's. The FSA is disabled whenever  $\overline{CS}$  is high (i.e., it presents a high impedance to the bus and ignores all bus activity.)

#### DATA.OUT.A, DATA.OUT.B (Pins 11 and 12)

Output data from the FIFO to the MBM generate circuitry, used to write data into the bubble device (active low).

DET.A+, DET.A-, DET.B+, DET.B- (Pins 6, 7, 8 and 9) Differential signal lines from the MBM detector.

#### DIO (Pin 17)

The Serial Bus data line (a bidirectional active high signal).

#### ENABLE.A, ENABLE.B (Pins 13 and 14)

TTL level outputs utilized as chip selects for other interface circuits. They shall be set and reset by the Command Decoder under instruction of the Controller (active low).

#### ERR.FLG (Pin 4)

An error flag used to interrupt the Controller to indicate that an error condition exists. It shall be an open drain active low signal.

#### RESET (Pin 16)

An active low signal that shall reset all flags and pointers in the FSA as well as disabling the chip as the CS signal does. The RESET pulse width must be 5 clock periods to assure the FSA is properly reset.

#### SELECT.IN (Pin 19)

An input utilized for time division multiplexing. An active low signal whose presence indicates that the FSA is to send or receive data from the Serial Bus during the next two clock periods.

#### SELECT.OUT (Pin 2)

22

The SELECT.IN pulse delayed by two clocks. It shall be connected to the SELECT.IN pin of the next FSA. It is delayed by two clocks because the FSA is a dual channel device. Channel A shall internally pass SELECT.IN to Channel B (delayed by one clock).

### 7242

#### Pin Description (Continued)

#### SHIFT.CLK (Pin 15)

A Controller generated clock signal that shall be used to clock data out of the bubble I/O Output Latch to the bubble module during a write operation and to cause bubble signals to be converted by the Sense Amp and clocked into the Bubble I/O Input Latch on a read. The FIFO pointers are reset by hardware or software resets or each time a command to read or write is received by the Command Decoder.

If a block length other than 272 bits is used in the no error correction mode, the FIFO pointers will not return to word zero at the end of each block transfer. This is of no consequence if one is not concerned about the absolute location of data in the FIFO. Keeping in mind that the FIFO is only 272 bits physically, any block length may be used up to and including 320.

#### **Functional Description**

The following is a brief description of each block of the 7242 FSA.

Serial Communications – The Serial Communications block handles all transfers on the Serial Bus and is shared by both channels of the FSA.

**Command Decoder** – The Command Decoder interprets commands by the Serial Communication logic and sets the appropriate command and enable lines. It also maintains FSA status, and generates various reset lines. **Bootstrap Loop Register** – The Bootstrap Loop Register is a 160 bit register that contains information detailing the location of bad loops in the MBM module. This data will enable FIFO I/O to ensure that bits are not loaded in the FIFO from bad loops, or written from the FIFO into bad loops. A logic zero (absence of a bubble) is written into bad loops.

**Error Correction Logic** — The Error Correction Logic contains the circuitry to implement a burst error correcting code capable of correcting any single burst error of length equal to or less than 5, anywhere in the 270 bit data stream, including the error correction code which is 14 bits in length. A Correction Enable bit may be set or reset via a special command. When reset, the entire error correction network is disabled and block length may vary from 270 bits. Error detection shall be accomplished on all data transfers (when enabled); however, correction cannot take place unless the FSA is operated in a buffered mode (i.e., an entire block is read prior to passing any data to the Controller).

**Internal Data Bus** – The Internal Data Bus is the main data link between the Serial Communications block and all other data sources in each half of the FSA.

I/O Latches, Flags, and Bus Control – Each channel of the FSA has its own Internal Data Bus, on which all data transfers are made. There is a Flag and a bidirectional Latch in each "I/O Latches – Flag" block. Only one Latch is used in a given operation and the Flag tells the Bus Controller whether or not the Latch is full. The Bus Controller monitors these flags, and other control signals, to determine when each device should have access to the Internal Data Bus. When a transfer is to be made, the appropriate devices are enabled, the Bus is enabled, and the transfer takes place synchronously by virtue **Bubble I/O** – The Bubble I/O consists of an integrated Sense Amplifier and an output driver. The Sense Amplifier consists of a sample-and-hold circuit and a differential, chopper stabilized comparator.

**Enables** — The ENABLE.A and ENABLE.B outputs are utilized as chip selects for external circuitry. To set an ENABLE line, the desired channel of the FSA must be selected and a Read or Write MBM, Set Enable Bit, Initialize, Read Collected Data, or Internally Correct Data command is sent. Any other command se-

#### of a transparent State Machine Sequencer.

quence will reset the ENABLE lines.

**FIFO** — The FIFO is a variable length First-In-First-Out buffer utilized to store data passing to and from the MBM module. The FIFO is logically 272 bits in length in the "no error correction" mode. It is 270 bits in the "error correction" mode, since 256 bits of data and a 14 bit error correction code must be used in this mode of operation.

#### Commands

23

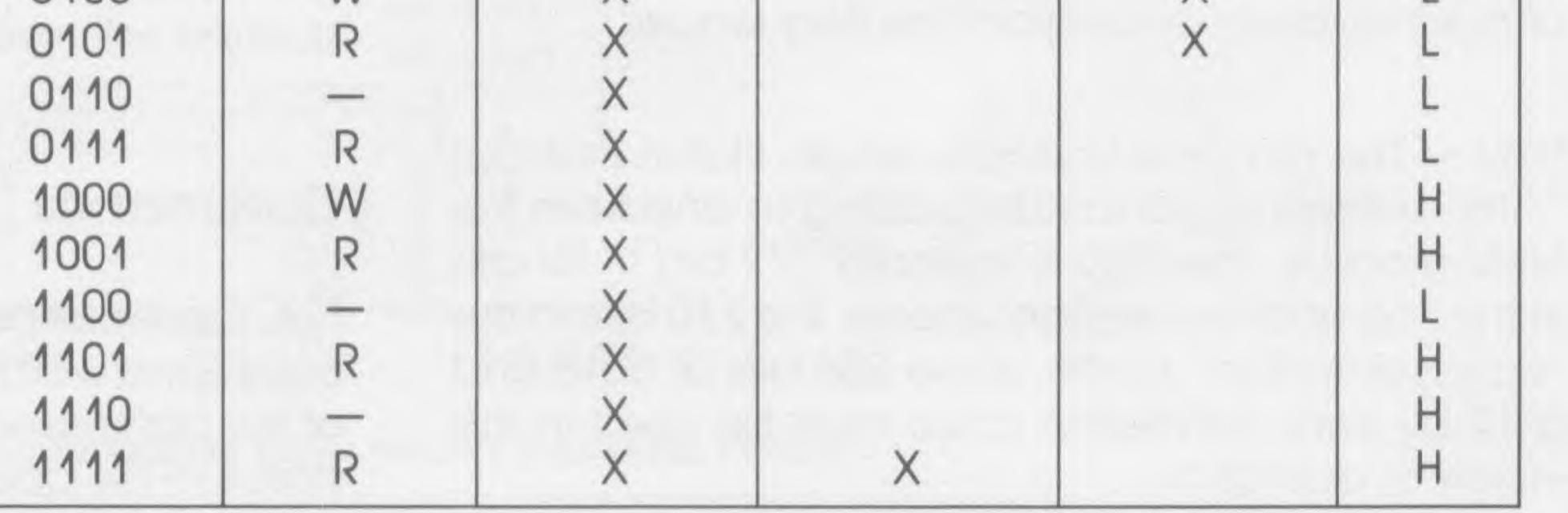

**FSA Commands** – The FSA shall receive a four bit command word via the Serial Bus. In addition, some of the commands require additional data bits, e.g., status to be passed.

### 7242

#### Commands (Continued)

serially. The four bits shall be interpreted as shown in Table 1. The effects on the Status bits, Correction Enable bit, and Enable pins are summarized in Table 2.

The following is a brief description of each command available in the 7242 FSA. **No Operation** – Deselects the chip and prevents further internal activity (default state for reset, unselected or unaddressed channels). Resets the FIFO and Bootloop pointers. The Enable pins (ENABLE.A and ENABLE.B) become inactive.

**Software Reset –** Resets all FIFO and Bootloop pointers and flags. Status flags, Error Correction Enable bit, error correction shift register, and the Enable pins become inactive.

Initialize – The chip is set to read data from the MBM Bootloop and pass it to the Controller. Resets

#### Table 1 Command Code Descriptions

| Code | Deserindian               | Data                      |              |

|------|---------------------------|---------------------------|--------------|

| Code | Description               | <b>Correction Enabled</b> | Not Enabled  |

| 0000 | No operation              | None                      | None         |

| 0001 | (Reserved)                |                           | _            |

| 0010 | Software Reset            | None                      | None         |

| 0011 | Initialize                | MBM Bootloop              | MBM Bootloop |

| 0100 | Write MBM Data            | 270 Bits In               | Variable     |

| 0101 | Read MBM Data             | 270 Bits Out              | Variable     |

| 0110 | Internally Correct Data   | None                      | _            |

| 0111 | Read Corrected Data       | 270 Bits Out              | _            |

| 1000 | Write Bootloop Register   | 160 Bits In               | 160 Bits In  |

| 1001 | Read Bootloop Register    | 160 Bits Out              | 160 Bits Out |

| 1010 | (Reserved)                |                           | _            |

| 1011 | (Reserved)                |                           |              |

| 1100 | Set Enable Bit            | None                      | None         |

| 1101 | Read ERR.FLG Status       | 1 Bit Out                 | 1 Bit Out    |

| 1110 | Set Correction Enable Bit | None                      | None         |

| 1111 | Read Status Register      | 8 Bits Out                | 8 Bits Out   |

#### Table 2 Command Function Summary

| Command Description | Command<br>Code | Data Flow<br>(R/W) | Reset FIFO<br>& Bootloop<br>Pointers | Reset Status<br>(Errors) | Reset Error<br>Correction<br>Logic | Enable |

|---------------------|-----------------|--------------------|--------------------------------------|--------------------------|------------------------------------|--------|

| No Operation        | 0000            | _                  | X                                    |                          |                                    | Н      |

| Software Reset      | 0010            | _                  | X                                    | X                        | X                                  | H      |

| Initialize          | 0010            | R                  | X                                    | X                        | X                                  | L      |

| Write MBM Data      | 0100            | W                  | X                                    |                          | X                                  | L      |

24

Read MBM Data Internally Correct Cata Read Corrected Data Write Bootloop Register Read Bootloop Register Set Enable Bit Read ERR.FLG Status Set Error Correction Enable Bit Read Status Register

### 7242

#### Commands (Continued)

the FIFO and Bootloop pointers, Error Correction Logic, and disables the Bootloop register, (so that it does not interfere with the data flow). The Enable pins become active in addressed channels.

Write MBM Data – Data input by the Controller is written into the good loops in use in the MBM (under control of the Bootloop register) each time a SHIFT.CLK is received. It also activates the Enable pins and resets the FIFO and Bootloop pointers. If the Correction Enable bit is set, the FSA computes the correction code and appends it to the data stream to be stored in the MBM (last 14 of 270 bits). (3) Send an Internally Correct Data command to the FSA. The FSA corrects the data without transferring it to the Controller. When finished, the FSA interrupts the Controller. At this point it can be determined whether or not the error is correctable. If so, a Read Corrected Data command may be sent to read the good data.

Internally Correct Data — Internally cycles the data through the error correction network and returns status as to whether or not the data is correctable.

**Read MBM Data** – This command activates the ENABLE pins and resets the FIFO and Bootloop pointers independent of the state of the Correction Enable bit. If the Correction Enable bit is reset, data, of block length dictated by 2 times the number of logic '1's in the Bootloop register, from the MBM is sensed and screened by the FSA Sense Amp and Bootloop register, and stored in the FIFO. As soon as one bit is guaranteed in the FIFO, simultaneous reading from the FIFO may be done by the Controller. The FIFO need not be emptied after each page is read, but one must insure that more than 272 bits of FIFO are not needed at any time during the transfer. Requires approximately 1400 clock cycles to complete. ERR.FLG will be inactive during internal cycling, but will return active at its completion. Also activates the ENABLE pins and resets the FIFO and Bootloop pointers.

**Read Corrected Data** – Cycles data through the error correction network with each Controller read (SELECT.IN at the FSA). At the end of 270 reads, status is available to indicate whether or not the data was successfully corrected. ERR.FLG acts as in Internally Correct Data. This command is required to read data corrected internally as well, but has no effect on the data read if it was successfully corrected. Activates the ENABLE pins and resets the FIFO and Bootloop pointers.

If the Correction Enable is set; data must be read in a buffered mode. First, a full block of data is read from the MBM. At that point the FIFO contains 270 bits of data. If an error is detected by the Error Correction network, the FSA raises the UNCORR.ERR and CORR.ERR flags which generate an interrupt to the controller. If no error is detected, the 270 bits of data may be read from the FIFO while sumultaneously reading and checking the next block of data from the MBM. When an error is detected the Controller may respond to the interrupt in one of 3 ways.

(1) Ignore it and try again (must make sure to reset the Error Correction shift register before a Write Bootloop Register – Contents of the FSA's Bootloop register are written with 160 bits from the Controller. The Controller must read the MBM Bootloop first, to determine which loops are good. The number of good bits in the 160 bit register is 135 if correction is used, and variable up to 160 if operating in the no correction mode. ENABLE pins become inactive and the FIFO and Bootloop pointers are reset.

**Read Bootloop Register –** As above except that data is read from the FSA Bootloop to the Controller.

Set Enable Bit – ENABLE pins become active for addressed channels, inactive for unaddressed channels. Also resets the FIFO and Bootloop pointers.

retry).

(2) Send a Read Corrected Data command to the FSA. This command will correct the data stream (if possible) and interrupt the Controller when the block has been read. At this time the Controller can send a Read Status command to see if the error was correctable (CORR.ERR) or uncorrectable (UNCORR.ERR). **Read ERR.FLG Status** – Reads the composite error status for addressed channels of the FSA. (The composite status is the logic OR of CORR.ERR, UNCORR.ERR and TIMER.R). The ERR.FLG pin is the logic NOR of both channels composite error status; ERR.FLG.A and ERR.FLG.B.) ENABLE pins become inactive and FIFO and Bootloop pointers are reset.

### 7242

#### **Commands (Continued)**

Set Error Correction Enable Bit — Enables the Error Correction Logic in addressed FSA's and disables it in unaddressed FSA's. ENABLE pins become inactive and FIFO and Bootloop pointers are reset. Furthermore, when this enable is set, the corresponding FIFO becomes a 270 bit FIFO (logically) instead of a 272 bit FIFO as in the no correction mode. FSA chain in shift register fashion via the FSA SELECT.IN/SELECT.OUT lines.

(2) Controller outputs a serial data stream on the DIO line beginning in the clock period following SYNC. Each bit in the stream corresponds to an address bit for a particular FSA (up to 16 channels). Each FSA, upon receiving SELECT.IN, will look for the presence or absence of a logic one on DIO in the clock period following receipt of SELECT.IN (a logic one indicates that the FSA shall accept the command).

**Read Status Register** — The 8 bit Status Word for the addressed FSA is output to the Controller. Only one FSA channel can be addressed at a time, or bus contention may result. ENABLE pins become inactive and error flags in the addressed FSA channel, and FIFO and Bootloop pointers are reset.

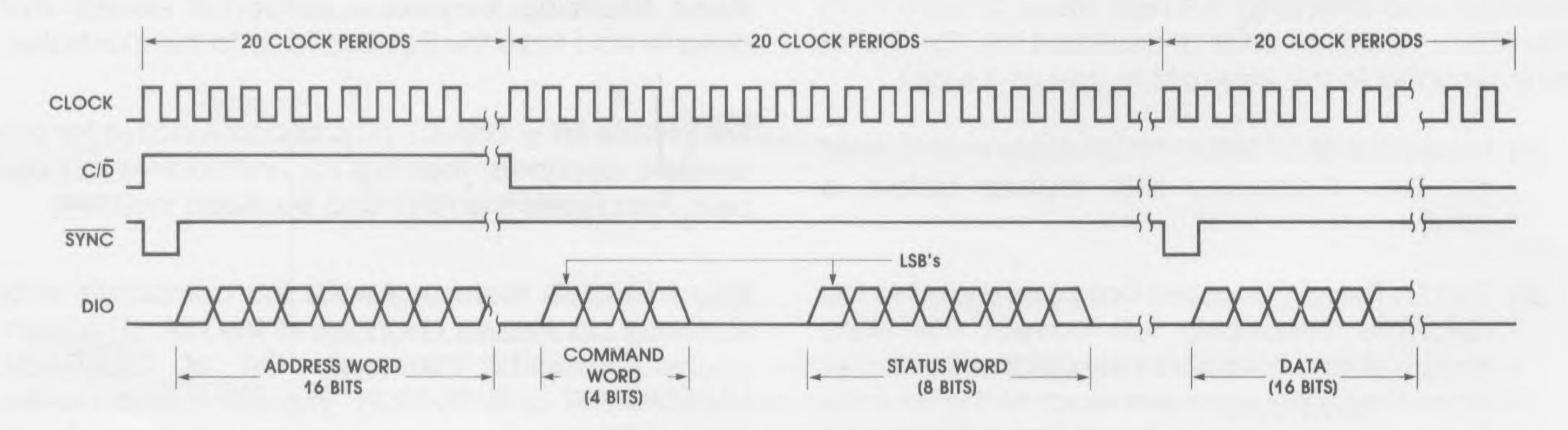

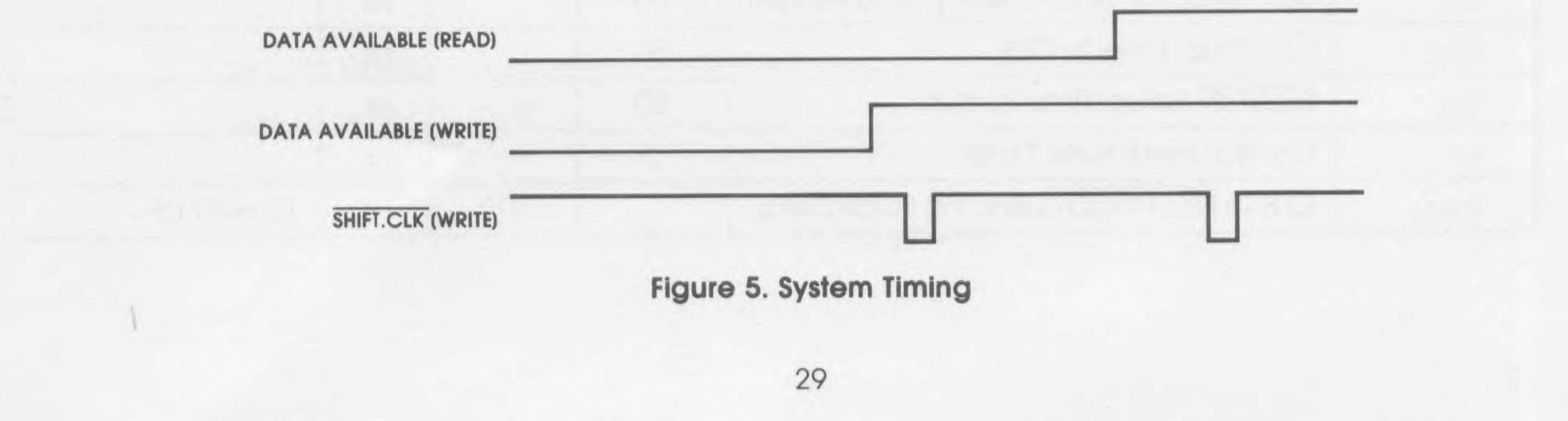

#### Serial Interface

**Command Sequence** — The FSA communicates with the Controller via a Serial Interface. The Controller/FSA Interface contains the following signals.

- (1) CLK

- (2) SELECT.IN (Formatter)

- (3) SELECT.OUT (Formatter)

- (4) SYNC (Controller)

- (3) Twenty clock periods after the first SYNC, the Controller sends  $C/\overline{D}$  low followed by a four bit command on the DIO line.

- (4) If the command is a Read Status command (1111), the addressed FSA returns 8 bits of Status starting 4 clock periods after the last command bit is received. Note that the Status is returned during this period for any FSA position. Therefore only one FSA channel should be addressed at a time to avoid contention.

- (5) If the command requires further data (see section on FSA Commands), more SYNC pulses are sent by the Controller. This will occur at integral multiples of 20 clock periods starting no sooner than 40 clocks after the first command SYNC

(5) DIO (6)  $C/\overline{D}$ (7) SHIFT.CLK (8) ERR.FLG

Commands from the Controller to the FSA shall take place in the following format (see Figure 1).

(1) Controller raises C/D flag indicating that a command is coming, and simultaneously outputs a SYNC pulse. This SYNC pulse is shifted down the pulse. Some number of SYNC periods may pass before the second SYNC to allow the FSA to set itself up and get data ready for the Controller. There are several possibilities:

(a) For the Read ERR.FLG Status command the second SYNC can occur 40 clocks after the first SYNC. This SYNC (or SELECT.IN) causes each addressed FSA to send the appropriate Status information. No further SYNC's (without C/D high) should be sent.

NOTE: STATUS INFO IS ONLY PRESENT ON BUS FOR THE READ STATUS COMMAND SEQUENCE.

**Figure 1. Command Sequences**

26

## 7242

#### Serial Interface (Continued)

(b) For the Read MBM Data (or Initialize) command the second SYNC must wait the appropriate number of SHIFT.CLOCK's to assure that valid data is available in the FIFO.

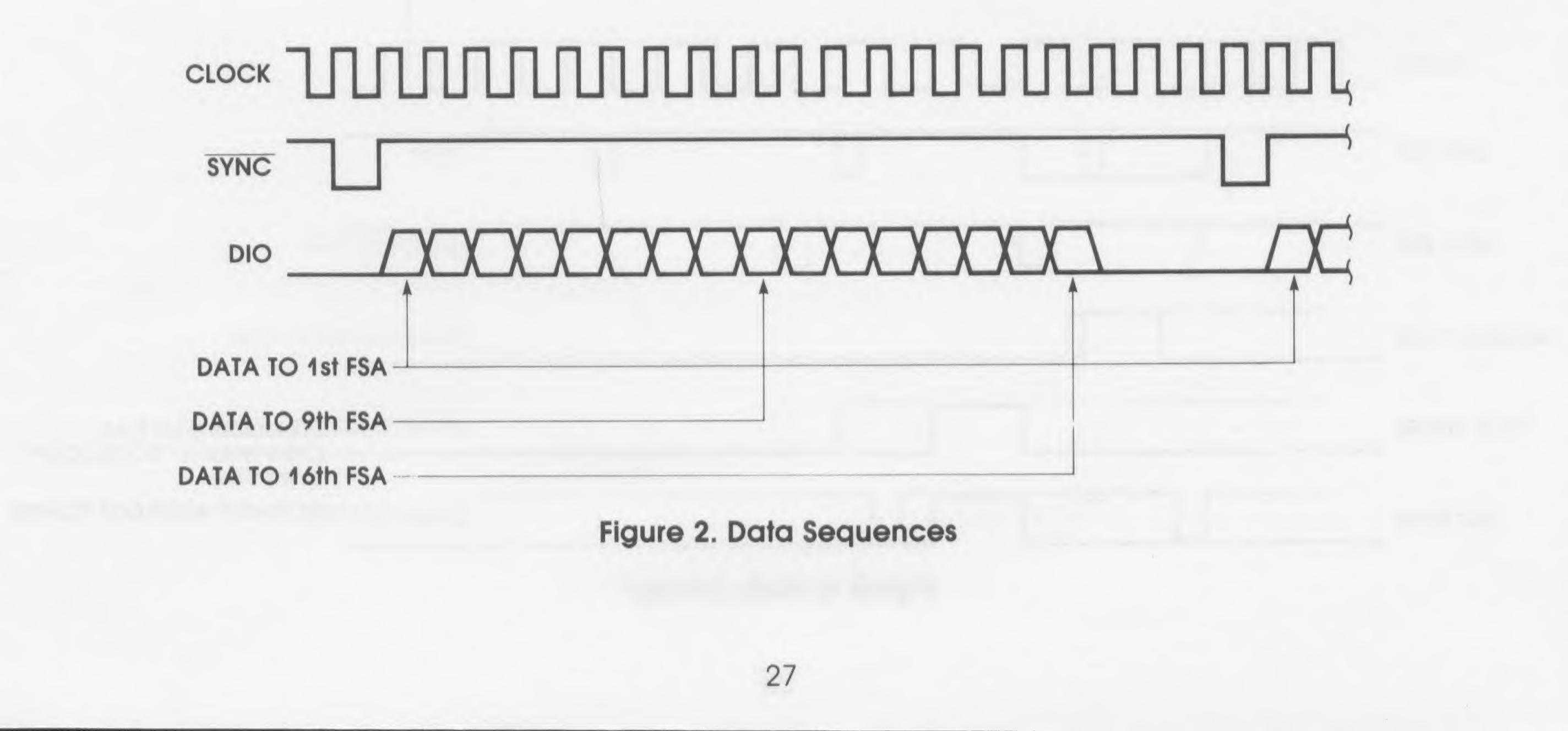

After this wait, each addressed FSA channel sends one bit of data on the DIO line for each SYNC (or SELECT.IN) pulse. Data Sequences – Bubble data shall be passed between the Controller and FSA's in the following fashion (see Figure 2).

#### (1) Controller outputs a SYNC pulse.

(2) Each FSA then outputs (inputs) a single bit on DIO after SYNC (SELECT.IN) has been clocked into its control section. Only previously enabled FSA's output (input) data and the Controller must know when to input (output) data bits.

(3) After 20 clocks, another SYNC pulse is output and

- (c) For the Read Bootloop Register command, the second SYNC can occur 60 clock cycles after the first SYNC. The data transfer then proceeds as in (b).

- (d) For the Write MBM Data or Write Bootloop commands, the DIO line is used to transfer data to the FSA on successive SYNC pulses. The first data bit can be transferred by a second <u>SYNC</u> pulse, 40 clock cycles after the first SYNC. (However, data to the MBM will not be available at the Dataout pins until 40 clock cycles after the SYNC which transferred it.) Each transfer to the addressed FSA will be initiated by a SYNC (or

- the sequence repeats until all data has been transferred.

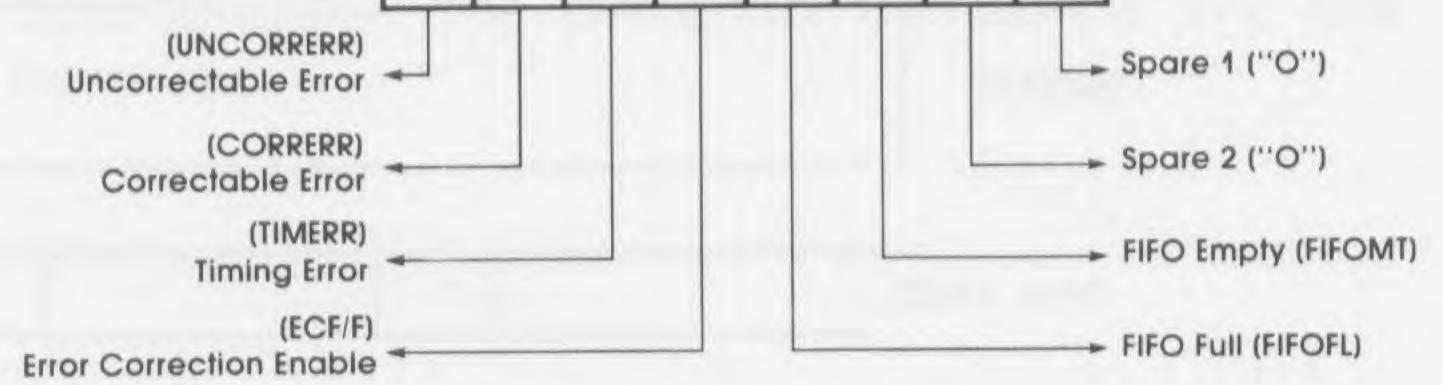

**Error Conditions** – Each FSA shall upon detection of an error set a Status bit and pull down ERR.FLG. This signal can be asynchronous to SYNC. Error Status bits shall be:

- (1) Correctable Error(2) Uncorrectable Error

- (3) Timing Error

The Status Word that shall be passed to the Controller after receipt of a Read Status command shall be in the following format:

|   | 1 |   |   | 1.1.1 |   |   |   |

|---|---|---|---|-------|---|---|---|

| 0 | 1 | 2 | 3 | 4     | 5 | 6 | 7 |

#### SELECT.IN).

(6) SYNC (SELECT.IN) precedes the data it transfers by 1 clock cycle. Data Transfers to or from the FSA's FIFO must contain the proper number of SYNC's (externally counted) or a timing error may occur (TIMERR flag will be set, causing an interrupt to the Controller).

NOTE: ERROR FLAGS SHALL BE RESET UPON BEING READ BY THE CONTROLLER OR BY A SOFTWARE RESET.

## 7242

#### **Bubble Interface**

**Bubble Interface** – Each Bubble Interface shall consist of a DATAOUT signal and a pair of differential inputs from the MBM detector bridge.

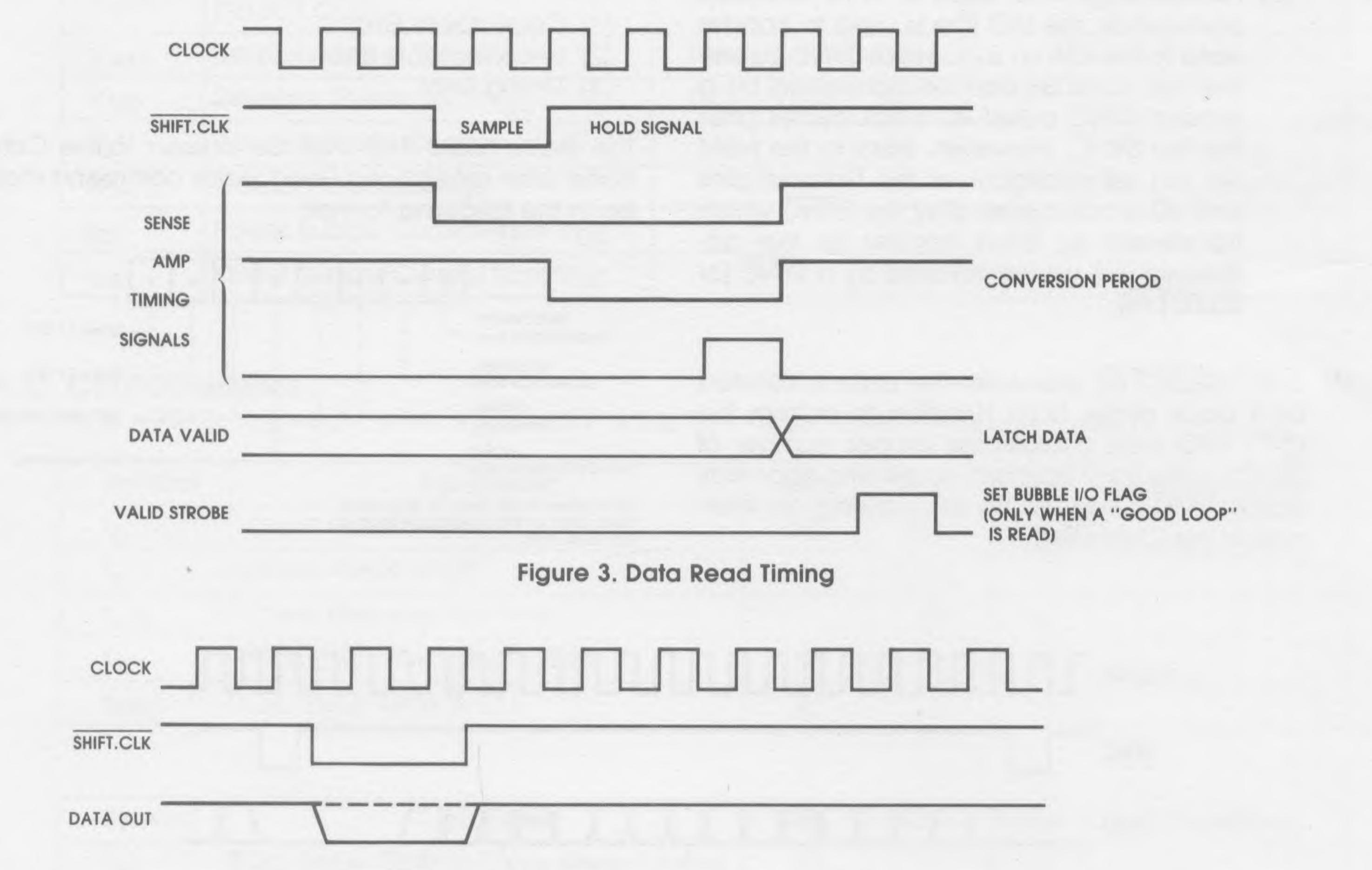

**Read Timing —** The timing for reading a bit from the memory shall be as follows (see Figure 3):

(3) Data is latched at end of conversion period in the Bubble Input latch, and will subsequently be loaded into the FIFO.

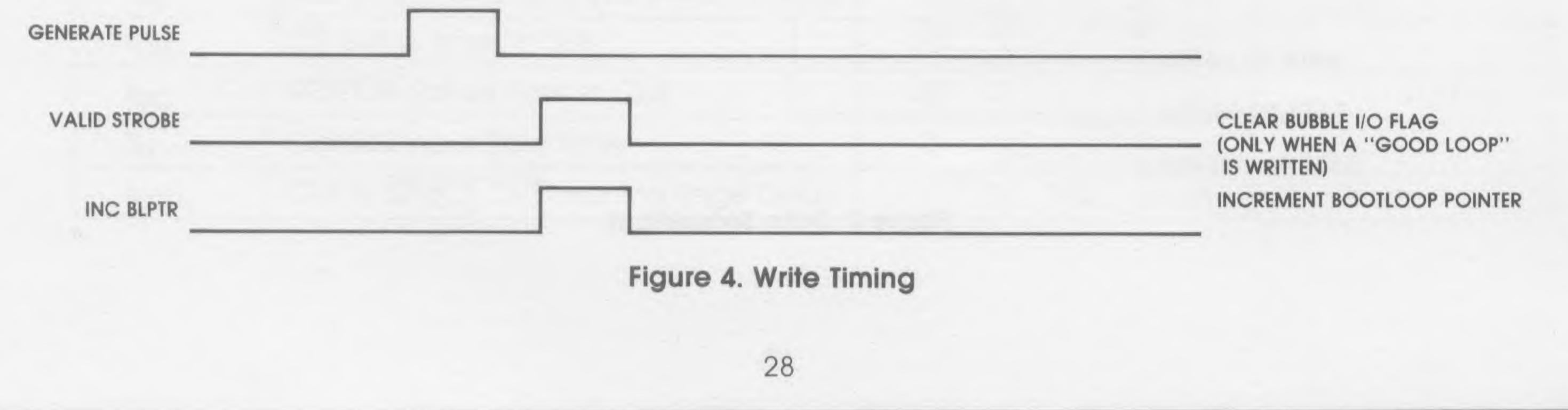

Write Timing — The timing for writing a bit from the FIFO shall be as follows (see Figure 4):

(1) Controller lowers SHIFT.CLK.

(2) Data is gated out of FSA by SHIFT.CLK.

(3) Controller outputs a generate pulse (to exter-

- (1) Controller outputs a SHIFT.CLK. FSA samples bubble signal during SHIFT.CLK and holds signal after trailing edge.

- (2) Trailing edge of SHIFT.CLK initiates signal conversion timing.

- nal logic; not to FSA).

- (4) Controller raises SHIFT.CLK. The DATA.OUT pin is forced high.

- (5) FIFO and Bootloop register are incremented after the trailing edge of SHIFT.CLK.

### 7242

#### **Bubble Interface (Continued)**

System Timing - The SYNC pulse (which denotes the beginning of a data transfer from Controller to Formatter or vice-versa) shall be synchronous with the beginning of a bubble memory field rotation. Due to timing constraints in the FSA, the following statements hold:

(1) Data read from the bubble memory into the

upon being read by the Controller or by a software reset being issued. The polynominal implemented is given below:

$$G(X) = 1 + X^{2} + X^{5} + X^{9} + X^{11} + X^{14}$$

#### **Data Format**

Data Format - Data into the FSA from the bubble memory shall be in the format described below. The following definitions apply:

- FSA shall not be available to the Controller until two field rotations after SHIFT.CLK.

- (2) Data cannot be written to the bubble memory until two field rotations after SYNC (see Figure 5).

#### **FSA Error Correction**

Error Correction - The error correction logic consists of a burst error correcting Fire code capable of correcting 5 or less bits in a single burst, the number of check bits is 14.\* Error correction/detection shall take place on each 256 bit data block. The FSA shall drop ERR.FLG each time a correctable or uncorrectable error is detected. ERR.FLG shall be set

$o_{\eta}$  = data from odd half of bubble device, loop  $\eta$  $e_n$  = data from even half of bubble device, loop  $\eta$

#### **Data Block Format:**

01e101e102e202e2 . . . 080e80080e80 320th bit 1st bit

When using correction, the first 270 good bits will be used, the last 14 of these are to be used for the error correcting code. The remaining 50 bits must be masked as "bad" bits in the FSA Bootloop register.

When operating without correction, any number of bits may be used by loading the Bootloop register appropriately. The preferred number is 272 bits however.

\*See "Error-Correcting Codes" by W. W. Peterson and E. J. Weldon, Jr., pp. 366-370, M.I.T. Press, 1972.

## 7242

#### **D.C. and Operating Characteristics** $T_A = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = 5.0V \pm 5\%$ , $V_{DD} = +12V \pm 5\%$

| Symbol | Deremaier                                              |      | Limits |             |      | Test Conditions               |  |

|--------|--------------------------------------------------------|------|--------|-------------|------|-------------------------------|--|

| Symbol | Parameter                                              | Min. | Typ.   | Max.        | Unit | Test Conditions               |  |

| VIL    | Input Low Voltage                                      | -0.5 |        | 0.8         | V    |                               |  |

| VIH    | Input High Voltage                                     | 2.0  |        | Vcc+<br>0.5 | V    |                               |  |

| Vol    | Output Low Voltage<br>(All Outputs except SELECT.OUT)  |      |        | 0.45        | V    | $I_{OL} = 3.2 \text{ mA}$     |  |

| Volso  | Output Low Voltage<br>(SELECT.OUT)                     |      |        | 0.45        | V    | $I_{OL} = 1.6 \text{ mA}$     |  |

| VOH    | Output High Voltage<br>(All Outputs except SELECT.OUT) | 2.4  |        |             | V    | I <sub>ОН</sub> =400 µА       |  |

| Vohso  | Output High Voltage<br>(SELECT.OUT)                    | 2.4  |        |             | V    | I <sub>ОН</sub> =200 µА       |  |

| VBIAS  | Detector Bias Voltage                                  | TBD  | 6.0    | TBD         | V    |                               |  |

| VTHR   | Detector Threshold                                     | TBD  | 0.004  | TBD         | V    |                               |  |

| 141    | Input Leakage Current                                  |      |        | 10          | μA   | $0 \leq V_{IN} \leq V_{CC}$   |  |

| IOFL   | Output Float Leakage                                   |      |        | 10          | μΑ   | $0.45 \le V_{OUT} \le V_{CC}$ |  |

| lcc    | Power Supply Current from Vcc                          |      |        | 120         | mA   |                               |  |

| IDD    | Power Supply Current from VDD                          |      |        | 30          | mA   |                               |  |

#### A.C. Characteristics

$T_A = 0^{\circ}C$  to +70°C,  $V_{CC} = 5.0V \pm 5\%$ ,  $V_{DD} = +12V \pm 5\%$ ,  $C_L = 150pF$ , unless otherwise noted.

| Symbol                          | Parameter                   | Min.   | Max.   | Unit | <b>Test Conditions</b> |

|---------------------------------|-----------------------------|--------|--------|------|------------------------|

| tp                              | Clock Period                | 200    | 2000   | ns   |                        |

| $t_{\phi}$                      | Clock Phase Width           | 0.4 tp | 0.6 tp |      |                        |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Time    |        | 30     | ns   |                        |

| tsic                            | SELECT.IN Setup Time to CLK | 50     |        | ns   |                        |

| tCDC                            | C/D Setup Time to CLK       | 50     |        | ns   |                        |

| Symbol           | Parameter                            | Min. | Max. | Unit | <b>Test Conditions</b> |

|------------------|--------------------------------------|------|------|------|------------------------|

| t <sub>DC</sub>  | DIO Setup Time to Clock (Read Mode)  | 50   |      | ns   |                        |

| tcsc             | CS Setup Time to CLK                 | 50   |      | ns   |                        |

| t <sub>RIC</sub> | RESET.IN Setup Time to CLK           | 50   |      | ns   |                        |

| t <sub>IH</sub>  | Control Input Hold Time              | 0    |      | ns   |                        |

| tCSOL            | CLK to SELECT.OUT Leading Edge Delay |      | 100  | ns   | $C_L = 50 \text{ pF}$  |

30

## 7242

#### A.C. Characteristics (Continued) $T_A = 0^{\circ}C$ to +70°C, $V_{CC} = 5.0V \pm 5\%$ , $V_{DD} = +12V \pm 5\%$ , $C_L = 150$ pF, unless otherwise noted.

| Symbol | Parameter                                             | Min. | Max. | Unit | <b>Test Conditions</b> |

|--------|-------------------------------------------------------|------|------|------|------------------------|

| tcsot  | CLK to SELECT.OUT Trailing Edge Delay                 |      | 80   | ns   | $C_L = 50 \text{ pF}$  |

| tCDV   | CLK to DIO Valid Delay*                               |      | 100  | ns   |                        |

| tCDH   | CLK to DIO Hold Time*                                 | 0    |      | ns   |                        |

| †CDE   | CLK to DIO Enabled from Float*                        |      | 100  | ns   |                        |

| †SIDE  | SELECT.IN Trailing Edge to DIO<br>Enabled from Float* | TBD  | 70   | ns   |                        |

| Symbol           | Parameter                             | Min. | Max. | Unit | Test Conditions                                                      |

|------------------|---------------------------------------|------|------|------|----------------------------------------------------------------------|

| t <sub>CDF</sub> | CLK to DIO Entering Float*            |      | 100  | ns   | $C_{L}(DIO) = 50 \text{ pF}, I_{OL} = 3.2 \text{ mA}$                |

| †DFSO            | DIO Float to SELECT.OUT Trailing Edge | TBD  |      | ns   | $C_L(DIO, SELECT.OUT) = 50 \text{ pF},$<br>$I_{OL} = 3.2 \text{ mA}$ |

| t <sub>CEF</sub> | CLK to ERR.FLG Delay                  |      | 300  | ns   | $R_L = 1.6K$ to $V_{CC}$                                             |

| tCEN             | CLK to ENABLE.A,B                     |      | 300  | ns   |                                                                      |

| Symbol        | Parameter                   | Min. | Max. | Unit | <b>Test Conditions</b> |

|---------------|-----------------------------|------|------|------|------------------------|

| tscdo         | SHIFT.CLK to DATAOUT Delay* |      | 200  | ns   |                        |

| <b>t</b> SCRV | SHIFT.CLK Recovery Time     | TBD  |      | ns   |                        |

| <b>t</b> SKEW | SHIFT.CLK to Sample Skew    |      | TBD  | ns   |                        |

| tscw          | SHIFT.CLK Width             | tp   |      | ns   |                        |

\*Write Mode

#### Capacitance $T_A = 25^{\circ}C$ , $V_{CC} = 0V$ , f = 1 MHz

| Symbol | Test               | Typ. | Max. | Unit | <b>Test Conditions</b> |

|--------|--------------------|------|------|------|------------------------|

| CIN    | Input Capacitance  |      | 10   | pF   |                        |

| Cout   | Output Capacitance |      | 10   | pF   |                        |

| CDIO   | DIO Capacitance    |      | 10   | pF   |                        |

31

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Absolute Maximum Ratings\*

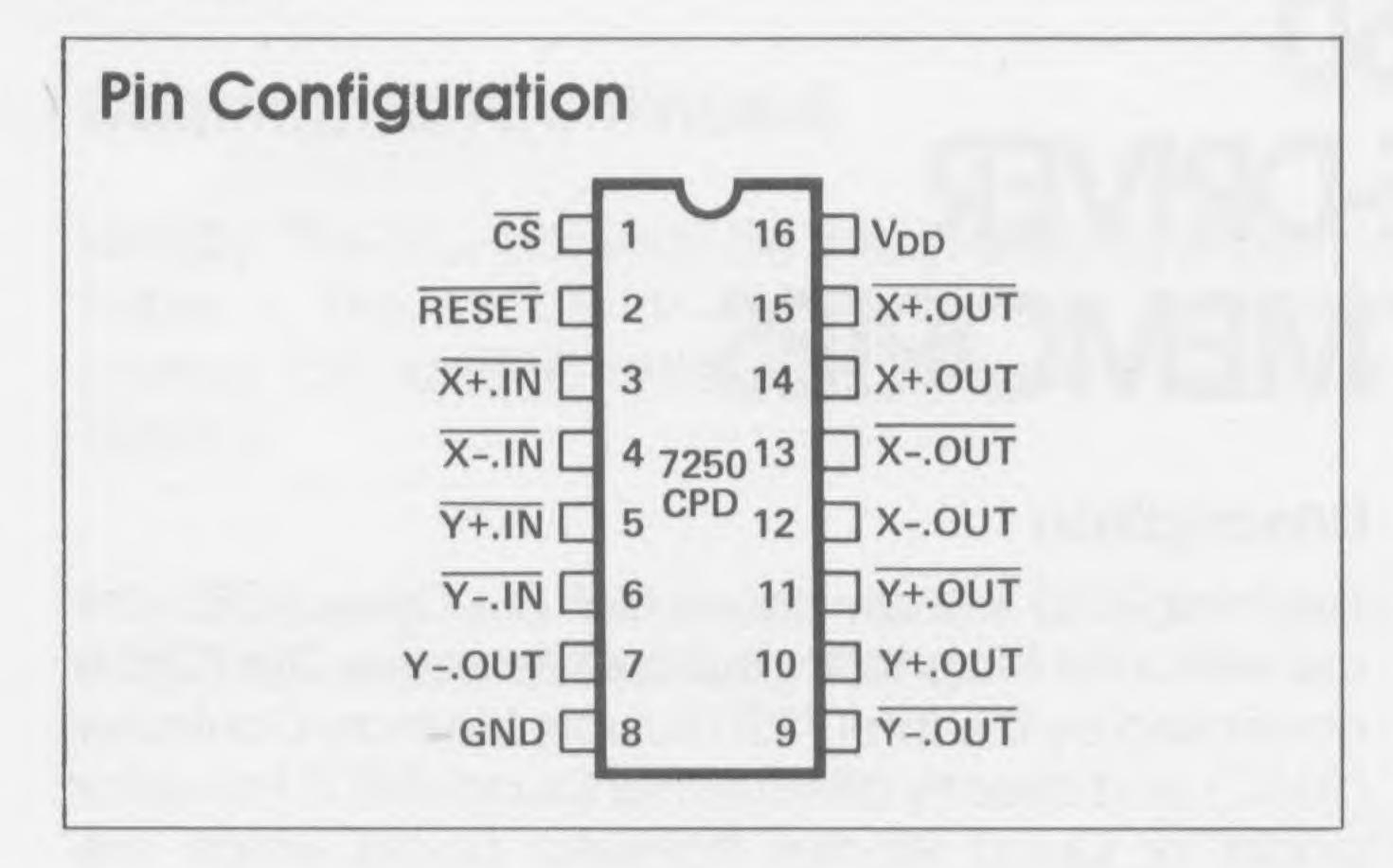

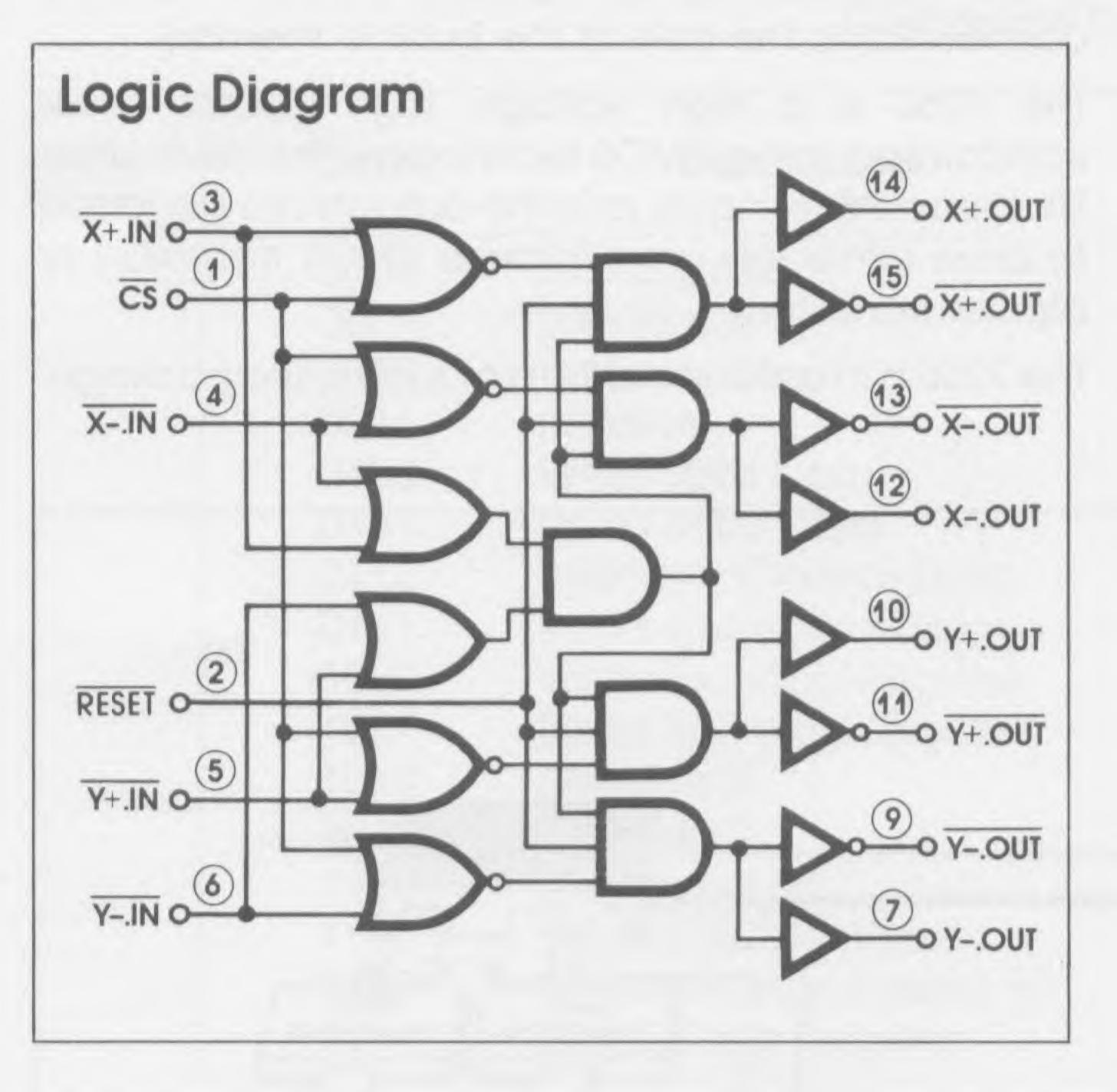

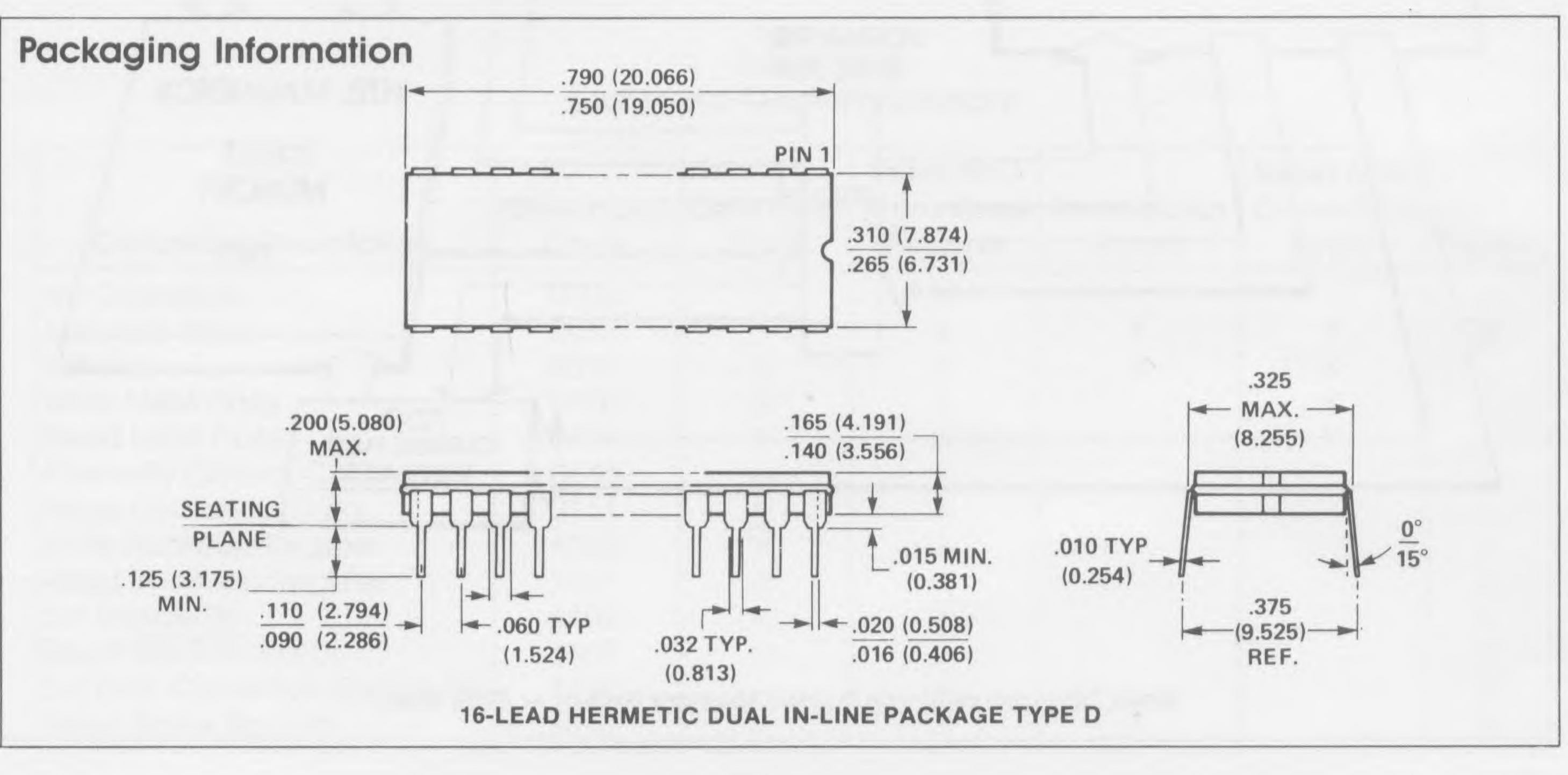

### 7250 COIL PRE-DRIVER FOR BUBBLE MEMORIES

### Features

- Ideal for Use with IM's Bubble Memories

- Very Low Power

### Description

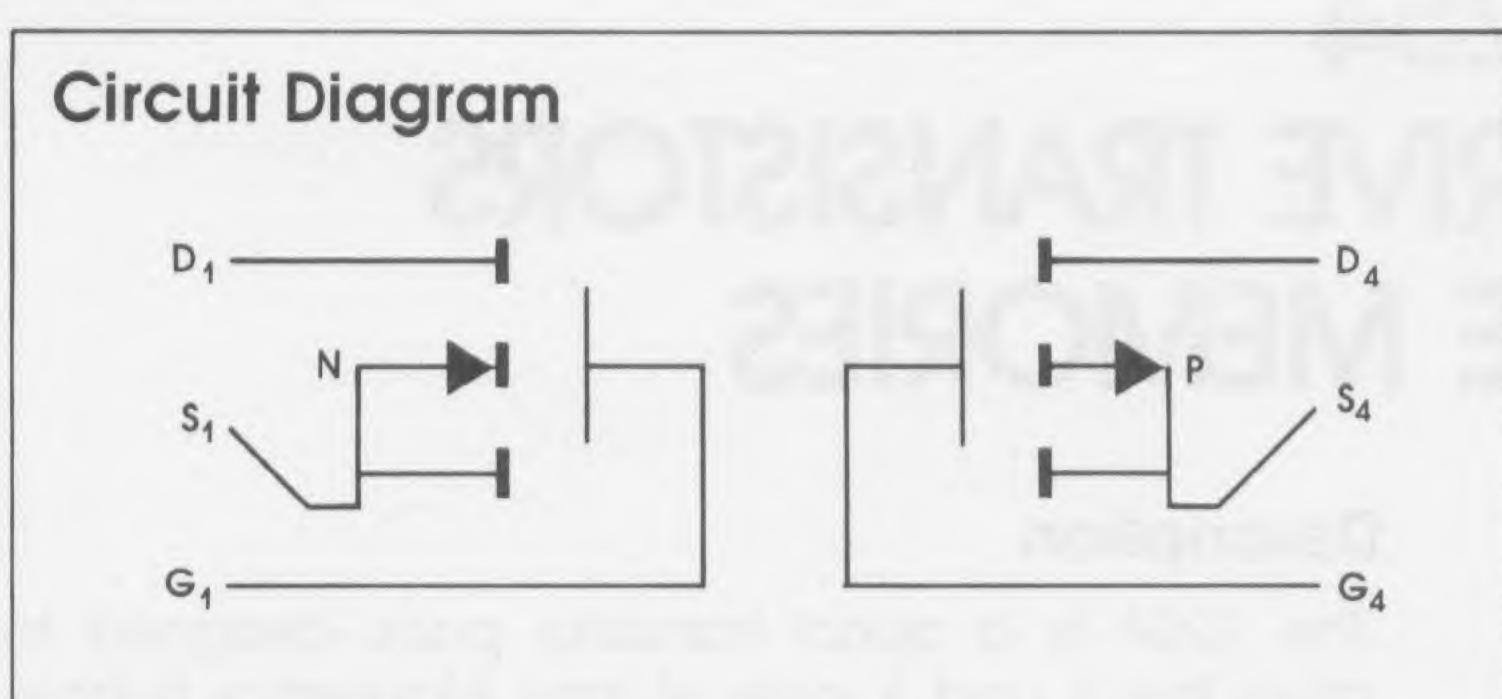

The Intel 7250 is a low power Coil Pre-Driver (CPD) for use with Intel Magnetics Bubble Memories. The 7250 is controlled by the Intel 7220 Bubble Memory Controller (BMC) and directly drives either Quad VMOS transistor packs or Quad Bipolar transistor packs which are connected to the coils of the bubble memory.

- Power Fail Reset for Maximum Protection of Bubble Memory

- TTL Compatible Inputs

- Only One Power Supply Required, +12V

- CMOS Technology

- Standard 16-Pin Dual In-Line Package

The 7250 is a high voltage, high current driver constructed using CMOS technology. The device has TL compatible inputs and the outputs are designed to drive either low on-resistance VMOS transistors or bipolar transistors.

The 7250 is in a standard 16-pin dual in-line package.

### 7250

### **Pin Description**

### CS (Pin 1)

Chip select. It is active low. When high chip is deselected and  $I_{DD}$  is significantly reduced.

### **RESET (Pin 2)**

Active low input from RESET.OUT of 7220 Controller results in removal of power from the chip so that bubble memory is protected in the event of power supply failure.

### X+.IN, X-.IN (Pins 3, 4)