XT-CF-lite Technical Reference

Technical reference manual for the XT-CF-lite board, currently version 1.0. See the main product page for general information, specifications, Bill of Materials, complete list of DIP switch settings and usage notes.

Downloads

- XT-IDE Universal BIOS (external link)

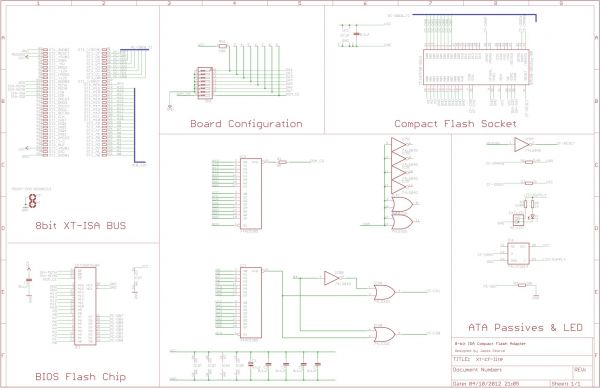

Schematic

Note: Switch position numbering is reversed in schematic.

Flash-based ROM

Functional Description

Boot ROM is provided via a SST39SF0x0A flash chip (DIP32) of 1Mb, 2Mb or 4Mb capacity, configured as a flat 32KB ROM (regardless of the chip size used). The ROM is configured via switches 1 to 4:

| Base Address | Sw1 | Sw2 | Sw3 | Sw4 |

|---|---|---|---|---|

| C000h | ON | ON | ON | ON |

| C800h | ON | OFF | ON | ON |

| D000h | ON | ON | OFF | ON |

| D800h | ON | OFF | OFF | ON |

| E000h | ON | ON | ON | OFF |

| E800h | ON | OFF | ON | OFF |

| F000h | ON | ON | OFF | OFF |

| F800h | ON | OFF | OFF | OFF |

| (Disabled) | OFF | - | - | - |

The ROM operates via a simple 8-bit comparitor IC2 (74520 or 74688) to generate chip-enable, gated by ISA AEN (DMA transfer), and is switched via Switch 1. The ROM operates entirely independently to the CompactFlash header, hence enabling a reduced component count to be fitted to provide only a ROM board functionality.

ISA Bus /MEMR and /MEMW are presented directly to the SST39SF flash chip, along with A[0..14] and D[0..7].

The XT-CF-lite uses the Lo-tech XT-CF flash utility for ROM programming.

Components Required for ROM Board Operation

The XT-CF-lite PCB can be constructed as a universal 32KB byte-programmable ROM board, without the CompactFlash functionality, by populating only:

| Part | Value | Device | Package | Qty | Farnell | Mouser |

|---|---|---|---|---|---|---|

| C1 | 47uF | CPOL-EUE2-5 | E2-5 | 1 | 8767114 | 140-REA470M1ABK0511P |

| C2 | 0.1uF | C-EUC0603 | C0603 | 1 | 1414610 | 81-GRM18R71C104MA01D |

| IC1 | SST39SF0x0A | SST39SF010ADIP32 | DIL32 | 1 | 1896595 | 804-39SF010A7CPHE |

| IC2 | 74AC520D | 74AC520D | SO20W | 1 | 1740268 | 595-SN74F521DWRG4 |

| R1 | 0R | R-EU_0207/10 | 0207/10 | 1 | 1700196 | 299-0-RC |

| RN1 | 10K | RN08 | RN-9 | 1 | 2112931 | 652-4609X-1LF-10K |

| SW1 | SW_DIP-8 | EDG-08 | 1 | 9471596 | 774-2068ST | |

| Socket | DIL32 | 1 | 1654375 | 571-1-390263-2 |

In this configuration, the board is functionally similar to the Lo-tech 8-bit ROM Board.

CompactFlash Adapter

Functional Description

The 3M CompactFlash header can support any type 1 or type 2 CompactFlash media, including microdrives. The media is powered directly from the 5V rail on the ISA bus.

The header is hard-wired for true-IDE mode operation, and therefore does not support hot-plug.

CompactFlash D[0..7] are connected directly to ISA Bus D[0..7] - there is no buffer present, since the CompactFlash specification provides for 8mA drive strength (the same as the SST39SF flash chip, which has been shown to work reliably in this configuration).

Since only D[0..7] are connected, the BIOS must perform a set-features command to enable 8-bit operation (which is supported by all CompactFlash media) before querying device ID.

Address Mappings

CompactFlash DA[0..2] are connected to ISA Bus A[1..3] - ISA Bus A0 is not decoded. This enables 16-bit instructions to be used (providing a performance advantage).

CompactFlash /CS0 and /CS1 are generated by a simple 8-bit comparitor IC3 (74520 or 74688), gated by ISA AEN (DMA transfer), IC 4 and 5 providing /CS0 or /CS1 (mutually exclusive) via ISA Bus A4 (see schematic). This provides access to all IDE registers within a port window of 1Fh:

| Base+ | Register |

|---|---|

| 00h | Data Register |

| 01h | Data Register (same as 00h) |

| 02h | Features Register |

| 04h | Sector Count Register |

| 06h | LBA Low Register |

| 08h | LBA Mid Register |

| 0Ah | LBA High Register |

| 0Ch | Device Register |

| 0Eh | Command Register |

| 1Ch | Device Control Register |

The base IO address is configured via switches 5 to 8 (see XT-CF-lite#IO_Range).

Code Examples

8-bit Port IO

8-bit Port IO provdes best platform compatibility. Data is collected from the data register using simple byte IO:

mov dx, 300h

mov cx, 32 ; unrolling offers big advantages

.ReadNextOword:

%rep 16 ; BYTEs

in al, dx ; Read BYTE

stosb ; Store BYTE to [ES:DI]

%endrep

loop .ReadNextOword

16-bit Port IO

16-bit Port IO offers significant performance advantage on 8088 hardware by reducing the loop code size and offloading part of the transfer to the bus interface unit, and further advantage on 8086 hardware by storing to memory using the full 16-bit datapath. However, not all early PC hardware implements 16-bit IO to 8-bit devices correctly, for example the AT&T 6300 presents data to the CPU byte-swapped.

mov dx, 300h

mov cx, 16 ; unrolling offers big advantages

.ReadNextOword:

%rep 8 ; WORDs

in ax, dx ; Read WORD via two bus-cycles

stosw ; Store WORD to [ES:DI]

%endrep

loop .ReadNextOword