## THE Z80 ADDRESS LINE TESTER

With the Z80 address line tester, all address lines on any logic board with a Z80 CPU, can be tested.

When the Z80 receives instruction hex 00 (a NOP), it does nothing except increment the program counter (PC) and reads the next instruction. If the next instruction is also a NOP, the microprocessor is forced to count through all 65,536 (2^16) possible addresses on its 16-bit address bus.

If you monitor the address bus lines with an oscilloscope, each address line will display a square wave, with a period twice that of the next lower address line. This gives you a predictable set of signals to trace through out the motherboard.

## **PROCEDURE**

- 1. Remove the Z80 CPU from the motherboard to be tested, and set it aside.

- 2. Install the Z80 ADDRESS LINE TESTER (known good Z80) in the motherboard to be tested. (Make sure that the notch faces in the same direction as the original Z80 CPU.)

- 3. Apply power to the motherboard.

- 4. Inspect the address lines for the wave forms listed in Table 24-1.

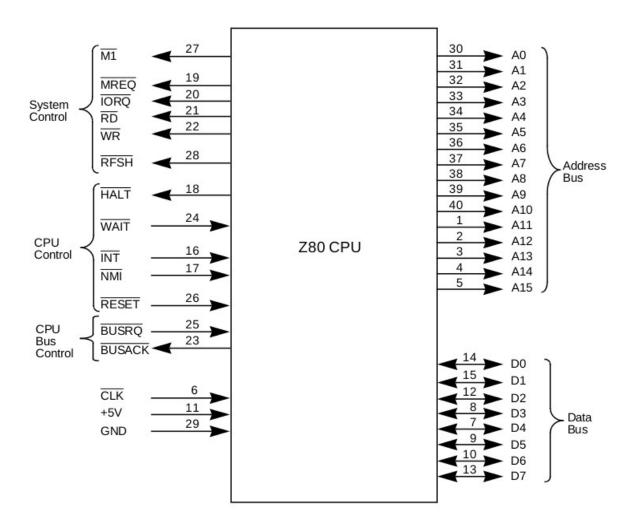

- 5. If you do not detect any pulses on the address lines, check the following signals:

Pin 11 +5VDC referenced to Pin 29 GND

- 6 Phase 0 clock

- 18 HALT (should be high)

- 24 WAIT (should be high)

- 26 RESET (should be high)

If any of these inputs are held in an incorrect state, the microprocessor will not work. Before continuing, correct any problems with these lines.

Table 24-1 Expected Wave forms

| Pin# | NAME    | WAVE FORM                    |

|------|---------|------------------------------|

| 1    | A11     | xx second period square wave |

| 2    | A12     | xx second period square wave |

| 3    | A13     | xx second period square wave |

| 4    | A14     | xx second period square wave |

| 5    | A15     | xx second period square wave |

| 6    | *CLK    |                              |

| 7    | D4      | Tied Low                     |

| 8    | D3      | Tied Low                     |

| 9    | D5      | Tied Low                     |

| 10   | D6      | Tied Low                     |

| 11   | +5VDC   |                              |

| 12   | D2      | Tied Low                     |

| 13   | D7      | Tied Low                     |

| 14   | D0      | Tied Low                     |

| 15   | D1      | Tied Low                     |

| 16   | *INT    |                              |

| 17   | *NMI    |                              |

| 18   | *HALT   |                              |

| 19   | *MREQ   |                              |

| 20   | *IORQ   |                              |

| 21   | *RD     |                              |

| 22   | *WR     |                              |

| 23   | *BUSACK |                              |

| 24   | *WAIT   |                              |

| 25   | *BUSRQ  |                              |

| 26   | *RESET  |                              |

| 27   | *M1     |                              |

| 28   | *RFSH   |                              |

| 29   | GND     |                              |

| 30   | A0      | xx second period square wave |

| 31   | A1      | xx second period square wave |

| 32   | A2      | xx second period square wave |

| 33   | A3      | xx second period square wave |

| 34   | A4      | xx second period square wave |

| 35   | A5      | xx second period square wave |

| 36   | A6      | xx second period square wave |

| 37   | A7      | xx second period square wave |

| 38   | A8      | xx second period square wave |

| 39   | A9      | xx second period square wave |

| 40   | A10     | xx second period square wave |