# TRS-80® MODEL 4/4P TECHNICAL REFERENCE MANUAL

CAT. NO. 26-2119

TRSDOS\* Version 6.2.0 Operating System:

© 1984 Logical Systems.

Licensed to Tandy Corporation

All Rights Reserved

Model 4/4P Technical Reference Manual; Software Part: § 1985 Tandy Corporation and Logical Systems All Rights Reserved

Reproduction or use, without express written permission from Tandy Corporation of any portion of this manual is prohibited While reasonable efforts have been taken in the preparation of this manual to assure its accuracy. Tandy Corporation assumes no liability resulting from any errors or omissions in this manual, or from the use of the information contained herein

TRSDOS is a registered trademark of Tandy Corporation

10 9 8 7 6 5 4 3 2 1

HARDWARE HARDWARE

### Part 1 / Hardware

| SECTION I   |                                        |

|-------------|----------------------------------------|

| 1.1         | Model 4 Theory of Operation            |

| 1.1.1       | Introduction                           |

| 1.1.2       | CPU and Timing                         |

| 1.1.3       | Buffering                              |

| 1.1.4       | Address Decoding                       |

| 1.1.5       | ROM                                    |

| 1.1.6       | RAM                                    |

| 1.1.7       | Keyboard                               |

| 1.1.8       | Video                                  |

| 1.1.9       | Real Time Clock                        |

| 1.1.10      | Cassette Circuitry                     |

| 1.1.11      | Printer Circuitry                      |

| 1.1.12      | I/O Connectors                         |

| 1.1.13      | Sound Option                           |

| 1.2         | Model 4 I/O BUS                        |

| 1.3         | Port Bits                              |

| SECTION II. |                                        |

| 2.1         | Model 4 Gate Array Theory of Operation |

| 2.1.1       | Introduction                           |

| 2.1.2       | Reset Circuit                          |

| 2.1.3       | CPU                                    |

| 2.1.4       | System Timing and Control Register     |

| 215         | Address Decode                         |

| 2.1.6       | ROM                                    |

| 2.1.7       | RAM                                    |

| 2.1.8       | Video Circuit                          |

| 2.1.9       | Keyboard                               |

| 2.1.10      | Real Time Clock                        |

| 2.1.11      | Line Printer Port                      |

| 2 1 12      | Graphics Port                          |

| 2.1.13      | Sound Port                             |

| 2.1.14      | I/O Bus                                |

| 2.1.15      | Cassette Circuit                       |

| 2.1.16      | FDC Circuit                            |

| 2.1.17      | RS-232C Circuit                        |

| SECTION III |                                        |

| 3.1         |                                        |

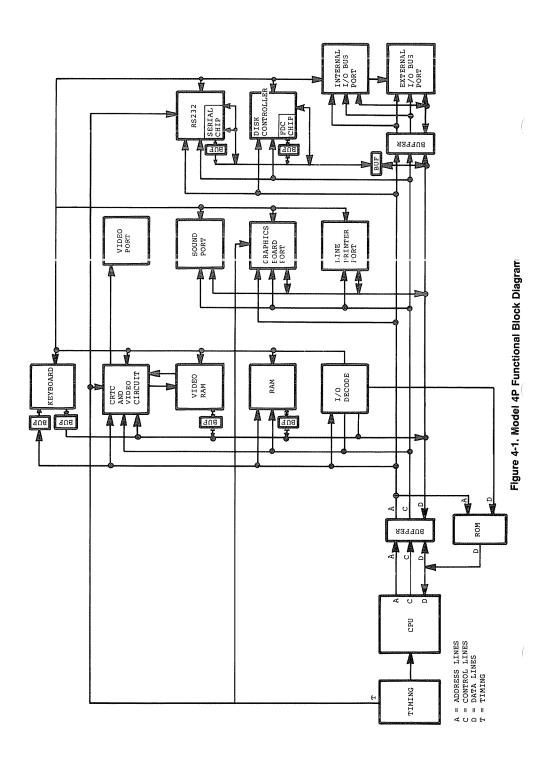

| 3.1         | Model 4P Theory of Operation           |

| 3.1.2       | Introduction                           |

| 3.1.3       | Reset Circuit                          |

| 3.1.4       | CPU                                    |

| 3.1.5       | System Timing                          |

| 3.1.6       | Address Decode                         |

| 3.1.7       | ROM                                    |

| 3.1.7       | RAM                                    |

| 3.1.9       | Video Circuit                          |

| 3.1.10      | Keyboard                               |

| 3.1.10      | Real Time Clock                        |

| 3.1.12      | Line Printer Port                      |

| 3.1.12      | Graphics Port                          |

| 3.1.13      | Sound                                  |

| 3.1.14      | I/O Bus Port                           |

| 3.1.15      | FDC Circuit                            |

| 3.1.10      | RS-232C Circuit                        |

| SECTION IV . |                                   |

|--------------|-----------------------------------|

| 4.2          | 4P Gate Array Theory of Operation |

| 4.2.1        | Introduction                      |

| 4.2.2        | Reset Circuit                     |

| 4.2.3        | CPU                               |

| 4.2.4        | System Timing                     |

| 4.2.5        | Address Decode                    |

| 4.2.6        | ROM                               |

| 4.2.7        | RAM                               |

| 4.2.8        | Video Circuit                     |

| 4.2.9        | Keyboard                          |

| 4.2.10       | Real Time Clock                   |

| 4.2.11       | Line Printer Port                 |

| 4.2.12       | Graphics Port                     |

| 4.2.13       | Sound                             |

| 4.2.14       | 1/O Bus Port                      |

| 4.2.15       | FDC Circuit                       |

| 4.2.16       | RS-232C Circuit                   |

| SECTION V    | Chip Specifications               |

|              |                                   |

INDEX

## SECTION I 4 THEORY OF OPERATION

### 1.1 MODEL 4 THEORY OF OPERATION

### 1.1.1 Introduction

The TRS-80 Model 4 Microcomputer is a self-contained desktop microcomputer designed not only to be completely software compatible with the TRS-80 Model III, but to provide many enhancements and features. System distinctions which enable the Model 4 to be Model III compatible include: a Z80 CPU capable of running at a 4 MHz clock rate, BASIC operating system in ROM (14K), memory-mapped keyboard, 64-character by 16-line memory-mapped video display, up to 128K Random Access Memory, cassette circuitry able to operate at 500 or 1500 baud, and the ability to accept a variety of options. These options include: one to four 5-1/4 inch double density floppy disk drives, one to four five megabyte hard disk drives, an RS-232 Serial Communications Interface, and a 640 by 240 pixel high resolution graphics board.

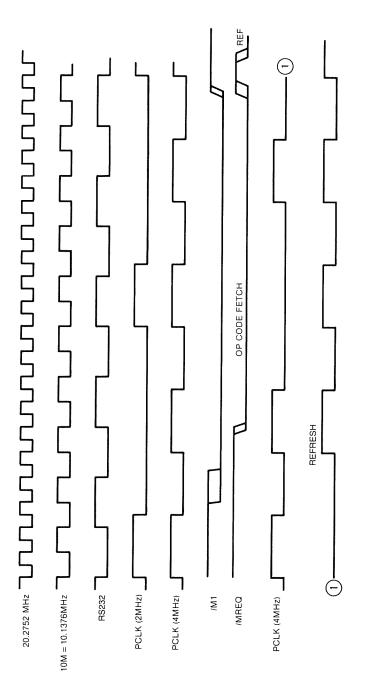

### 1.1.2 CPU and Timing

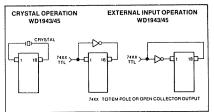

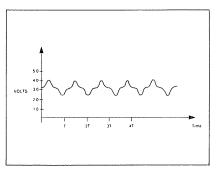

The central processing unit of the Model 4 microcomputer is the Z80-A microprocessor — capable of running at either a two (2.02752) or four (4.05504) MHz clock rate. The main CPU timing comes from the 20 MHz (20.2752 MHz) crystal-controlled oscillator, Y1 and Q1. There is an additional 12 MHz (12.672 MHz) oscillator, Y2 and Q2, which is necessary for the 80 by 24 mode of video operation. The oscillator outputs are sent to two Programmable Array Logic (PAL) circuits, U3 and U4, for frequency division and routing of appropriate timing signals.

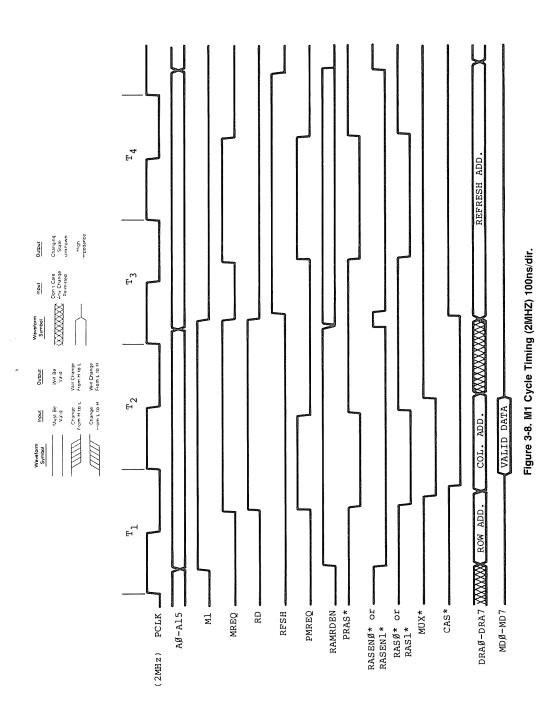

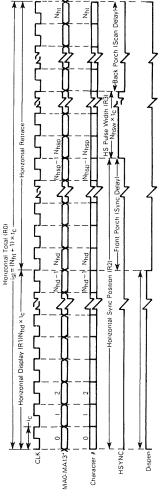

PAL U3 divides the 20 MHz signal by five for 4 MHz CPU operation, by ten for a 2 MHz rate, and slows the 4 MHz clock for the M1 Cycle (See Figure 1-3) U3 also divides the master clock by four to obtain a 5 MHz clock to be sent to the RS-232 option connector as a reference for the baud rate generator. PAL U4 selects an appropriate 10 MHz or 12 MHz clock for the video shift clock, and using divider U5 provides additional timing signals to the video display circuitry (See Fig. 1-4).

Hex latch U18 is clocked from the 20 MHz clock, and is used to provide MUX and CAS timing for the dynamic

memory circuits. Also, with additional gates from U16, U19, U20, U31, and U32, this chip provides the wait circuitry necessary to prevent the CPU from accessing video RAM during the active portion of the display. This is done by latching the data for the video RAM and simultaneously forcing the Z80 CPU into a "WAIT" state and is necessary to eliminate undesirable "hashing" of the video display (See Fig. 1-4).

### 1.1.3 Buffering

Low level signals from and to the CPU need to be buffered, or current amplified in order to drive many other circuits. The 16 address lines are buffered by U55 and U56, which are unidirectional buffers that are permanently enabled. The eight data lines are buffered by U71. Since data must flow both to and from the CPU, U71 is a bi-directional buffer which can go into a three-state condition when not in use. Both direction and enable controls come from the address decoding section.

The clock signal to the CPU (from PAL U3) is buffered by active pullup circuit Q3 RESET and WAIT inputs to the CPU are buffered by U17 and U46. Control outputs from the Z80 (M1\*, RD\*, WR\*, MREQ\*, and IORQ\*) are sent to PAL U58, which combines these into other appropriate control signals consistent with Model 4's architecture. Other than MREQ\*, which is buffered by part of U38, the raw control signals go to no other components, and hence require no additional buffering.

### 1.1.4 Address Decoding

The address decoding section is divided into two subsections: Port address decoding and Memory address decoding.

In port address decoding, low order address lines (some combined through a portion of U32) are sent to the address and enable inputs of U48, U49, and U50. U48 is also enabled by the IN\* signal, which means that is decodes port input signals, while U49 decodes port output signals. A table of the resulting port map is shown below:

| Read Function          | Write Function                                                                            |  |

|------------------------|-------------------------------------------------------------------------------------------|--|

| Cassette In, Mode Read | Cassette Out, resets cassette data latch                                                  |  |

| Read Printer Status    | Output to Printer                                                                         |  |

| - reserved -           | Drive Select latch                                                                        |  |

| FDC Data Reg.          | FDC Data Reg.                                                                             |  |

| FDC Sector Reg.        | FDC Sector Reg.                                                                           |  |

| FDC Track Reg.         | FDC Track Reg.                                                                            |  |

|                        | Cassette In, Mode Read  Read Printer Status  - reserved -  FDC Data Reg.  FDC Sector Reg. |  |

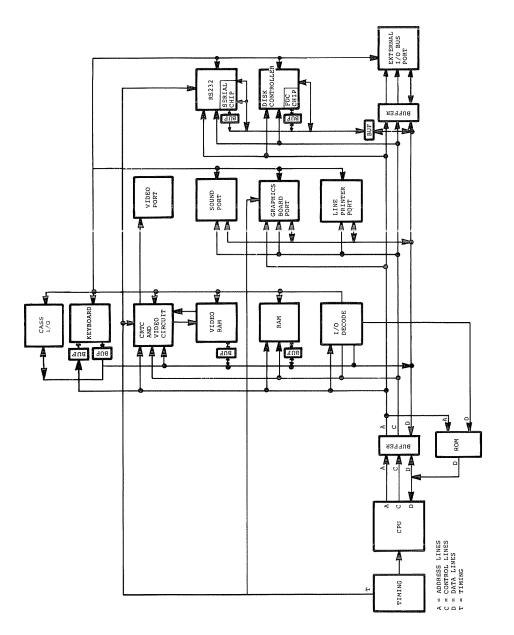

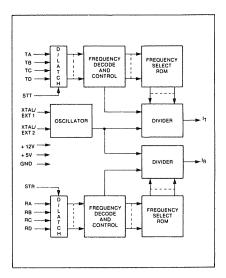

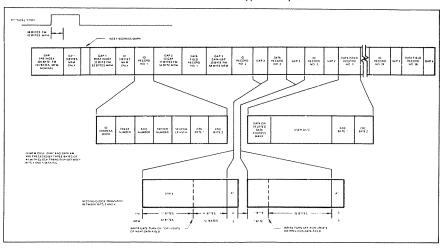

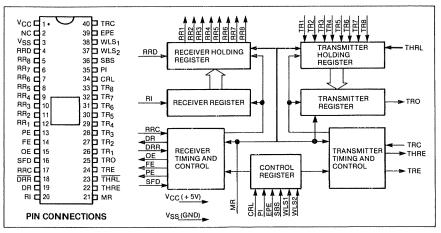

FIGURE 1-1. MODEL 4 BLOCK DIAGRAM

(1) FØ FDC Status Reg. EC · EF Resets RTC Int. (2) EB Rovr Holding Reg. (2) EA UART Status Reg. (2) E9 - reserved -(2) E8 Modem Status E4 - E7 Read NMI Status E0 - E3 Read INT Status (3) CF **HD** Status (3) CE HD Size/Drv/Hd (3) CD HD Cylinder high (3) CC HD Cylinder low (3) CB **HD Sector Number** (3) CA **HD Sector Count** (3) C9 HD Error Reg. (3) C8 HD Data Reg. (3) C7 HD CTC channel 3 (3) C6 HD CTC channel 2 (3) C5 HD CTC channel 1 (3) C4 HD CTC channel 0 (3) C2 - C3 HD Device ID Reg. (3) C1 HD Control Reg. (3) CO HD Wr. Prot. Reg. 94 - 9F - reserved -(4) 90 - 93 - reserved -(5) 8C - 8F Graphics Sel. 2 88 CRTC Data Reg. 88 CRTC Control Reg. 89 CRTC Data Reg. 88 CRTC Control Reg 84 - 87 - reserved -(5) 83 - reserved -(5) 82 - reserved -(5) 81 Graphics Ram Rd (5) 80 - reserved -

FDC Command Reg. Mode Output latch Xmit Holding Reg. UART/Modem control Baud Rate Register Master Reset/Enable UART control reg. Write NMI Mask reg. Write INT Mask reg. **HD** Command HD Size/Drv/Hd HD Cylinder high HD Cylinder low **HD Sector Number HD Sector Count** HD Write Precomp. HD Data Reg. HD CTC channel 3 HD CTC channel 2 HD CTC channel 1 HD CTC channel 0 - reserved -HD Control Reg. - reserved -· reserved -Sound Option Graphics Sel. 2 CRTC Data Reg. CRTC Control Reg. CRTC Data Reg. CRTC Control Reg. Options Register Gra. X Reg. Write Gra. Y Reg. Write Graphics Ram Wr.

Gra. Options Reg. Wr

Notes: (1) Valid only if FDC option is installed

(2) Valid only if RS-232 option is installed

(3) Valid only if Hard Disk option is installed

(4) Valid only if sound option is installed

(5) Valid only if High Resolution Graphics option is installed

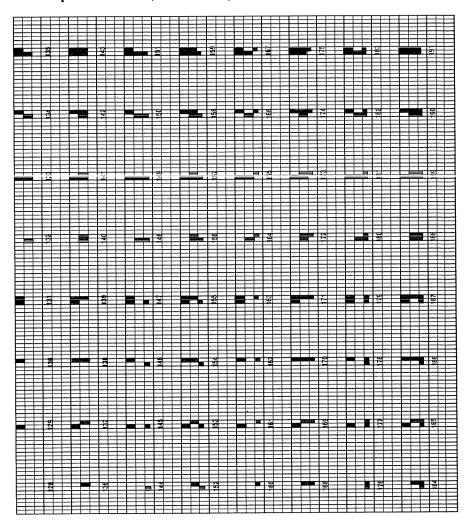

Following is a Bit Map of the appropriate ports in the Model 4. Note that this is an "internal" bit map only. For bit maps of the optional devices, refer to the appropriate section of the desired manual.

### Model 4 Port Bit Map

| Port               | D7             | D6                | D5                 | D4                 | D3               | D2               | D1               | D0               |

|--------------------|----------------|-------------------|--------------------|--------------------|------------------|------------------|------------------|------------------|

| FC · FF            | Cass           |                   |                    |                    |                  |                  |                  | Cassette         |

| (READ)             | data<br>500 bd |                   | (MIF               | RORofPe            | ORT EC)          |                  |                  | data<br>1500 bd  |

| FC-FF              |                | (1)               | lote, also resets  | cassette data la   | atch)            |                  | cass.            | cassette         |

| (WRITE)            | ×              | ×                 | ×                  | ×                  | ×                | ×                | out              | data out         |

| F8 - FB<br>(READ)  | Prntr<br>BUSY  | Prntr<br>Paper    | Prntr<br>Select    | Prntr<br>Fault     | x<br>x           | x<br>x           | x<br>x           | x<br>x           |

| +8 - FB<br>(WRITE) | Prntr<br>D7    | Prnu<br>D6        | Prnu<br>D5         | Printi<br>D4       | Printi<br>D3     | Printi<br>D2     | Prnu<br>D1       | Prntr<br>D0      |

| EC-EF              |                |                   | (Any Read          | causes reset of l  | Real Time Cloc   | k Interrupt)     |                  |                  |

| EC - EF<br>(WRITE) | x<br>x         | CPU<br>Fast       | x<br>x             | Enable<br>EX I/O   | Enable<br>Altset | Mode<br>Select   | Cass<br>Mot On   | x<br>x           |

| E0 · E3<br>(READ)  | x<br>x         | Receive<br>Error  | Receive<br>Data    | Xmit<br>Empty      | 10 Bus<br>Int    | RTC<br>Int       | C Fall<br>Int    | C Rise<br>Int    |

| E0 - E3<br>(WRITE) | x<br>x         | Enable<br>Rec Err | Enable<br>Rec Data | Enable<br>Xmit Emp | Enable<br>10 Int | Enable<br>RT Int | Enable<br>CF Int | Enable<br>CR Int |

| 90 - 93<br>(WRITE) | x<br>x         | x<br>x            | x<br>x             | x<br>x             | x<br>x           | x<br>x           | x<br>x           | Sound<br>Bit     |

| 84 - 87<br>(WRITE) | Page           | Fix Upr<br>Memory | Memory<br>Bit 1    | Memory<br>Bit 0    | Invert<br>Video  | 80/64            | Select<br>Bit 1  | Select<br>Bit 0  |

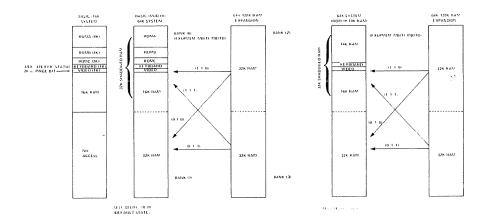

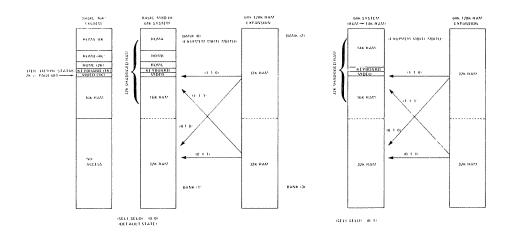

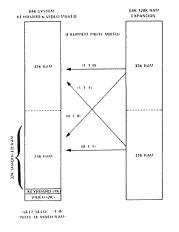

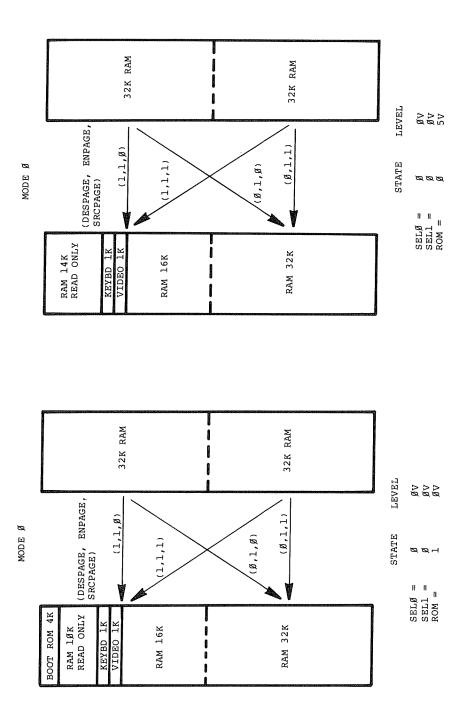

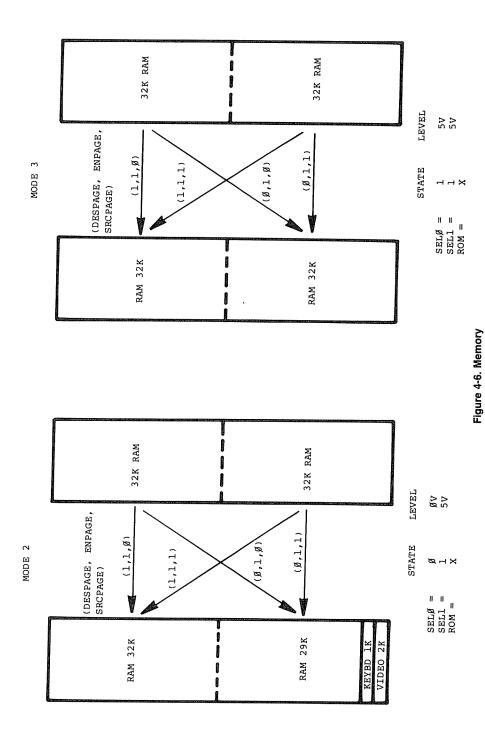

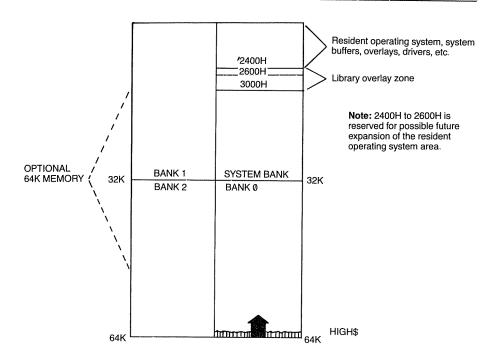

Memory mapping is accomplished by PAL U59 in the Basic 16K or 64K computer. In a 128K system, PAL U72, along with the select and memory bits of the options register, also enter into the memory mapping function.

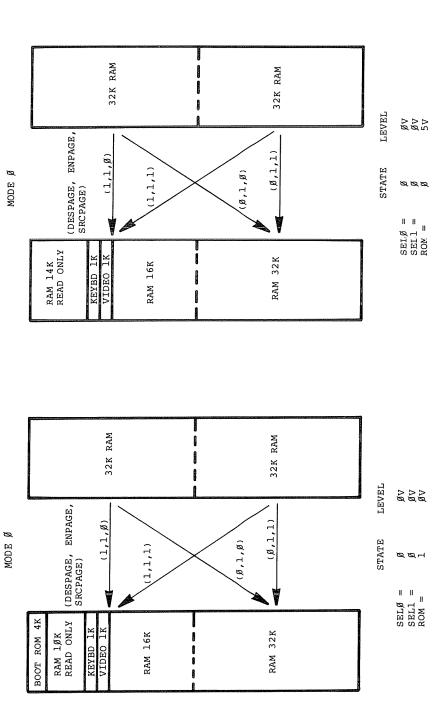

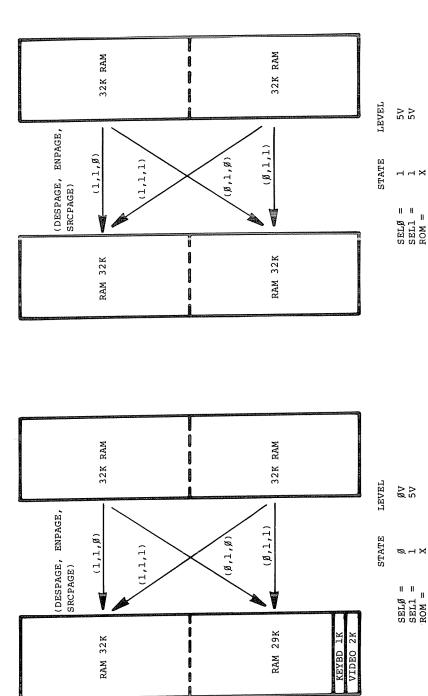

Four memory maps are listed below. Memory Map I is compatible with the Model III. Note that there are two 32K banks in the 64K system, which can be interchanged with either position of the upper two banks of a 128K system. The 128K system has four moveable 32K banks. Also note, in the Model III mode, that decoding for the printer status read (37E8 and 37E9 hexadecimal) is accomplished by U93 and leftover gates from U40, U46, U51, U54, U60, and U62.

### Memory Map I - Model III Mode

|   | 0000 - 1FFF | ROM A (8K)                            |

|---|-------------|---------------------------------------|

|   | 2000 - 2FFF | ROM B (4K)                            |

|   | 3000 - 37FF | ROM C (2K) — Less 37E8 - 37E9         |

|   | 37E8 - 37E9 | Printer Status Port                   |

|   | 3800 - 3BFF | Keyboard                              |

|   | 3C00 - 3FFF | Video RAM (Page bit selects 1K of 2K) |

|   | 4000 - 7FFF | RAM (16K system)                      |

| , | 4000 - FEFF | RAM (64K system)                      |

### Memory Map II

| 0000 - 37FF | RAM (14K)      |                     |

|-------------|----------------|---------------------|

| 3800 - 3BFF | Keyboard       |                     |

| 3C00 - 3FFF | Video RAM      |                     |

| 4000 – 7FFF | RAM (16K)      | End of one 32K Bank |

| 8000 - FFFF | RAM (32K)      | Second 32K Bank     |

|             | Memory Map III |                     |

| 0000 7FFFF  | RAM (32K)      | End of One 32K Bank |

| 8000 F3FF   | RAM (29K)      | Second 32K Bank     |

| F400 F7FF   | Keyboard       | Occoria dell' Baril |

| F800 - FFFF | Video RAM      |                     |

|             | Memory Map IV  |                     |

| 0000 - 7FFF | RAM (32K)      | One 32K Bank        |

| 8000 - FFFF | RAM (32K)      | Second 32K Bank     |

|             |                |                     |

(See Figure 1-2 for 128K Maps)

### 1.1.5 ROM

The Model 4 Microcomputer contains 14K of Read Only Memory (ROM), which is divided into an 8K ROM (U68), a 4K ROM (U69), and a 2K ROM (U70). ROMs used have three-state outputs which are disabled if the ROMs are deselected. As a result, ROM data outputs are connected directly to the CPU data bus and do not use data buffer U71, which is disabled during a ROM access.

ROMs are Model III compatible and contain a BASIC operating system, as well as a floppy disk boot routine. The enable inputs to the ROMs are provided by the address decoding section, and are present only in the Model III mode of operation.

### 1.1.6 RAM

Three configurations of Random Access Memory are available on the Model 4: 16K, 64K, and 128K. The 16K option uses 4116 type, 16K by 1 dynamic RAMs, which require three supply voltages (+12 volts, +5 volts, and -5 volts). The 64K and 128K options use 6665 type, 64K by 1 dynamic RAMs, which require only a single supply voltage (+5 volts). The proper voltage for each option is provided by jumpers.

Dynamic RAMs require multiplexed incoming address lines. This is accomplished by ICs U63 and U76. Output data from RAMs is buffered by U64. With the 128K option, there are two rows of the 64K by 1 RAM ICs. The proper row is selected by the CAS\* signal from PAL U72.

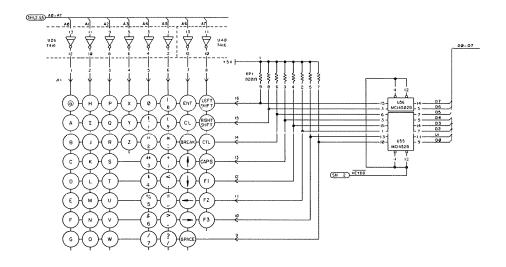

### 1.1.7 Keyboard

The Model 4 Keyboard is a 70-key sculptured keyboard, scanned by the microprocessor. Each key is identified by its column and row position. Columns are defined by address lines A0 - A7, which are buffered by open-collector drivers U29 and U30. Data lines D0 - D7 define the rows and are buffered by CMOS buffers U44 and U45. Row inputs to the buffers are pulled up by resistor pack RP 1, unless a key in the current column being scanned is depressed. Then, the row for that key goes low.

### 1.1.8 Video

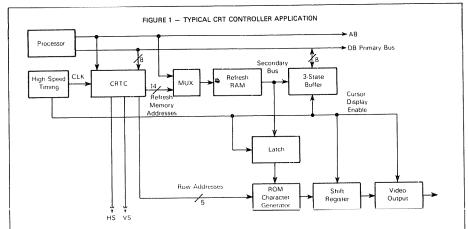

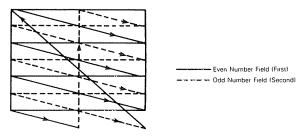

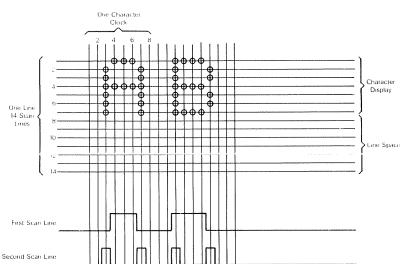

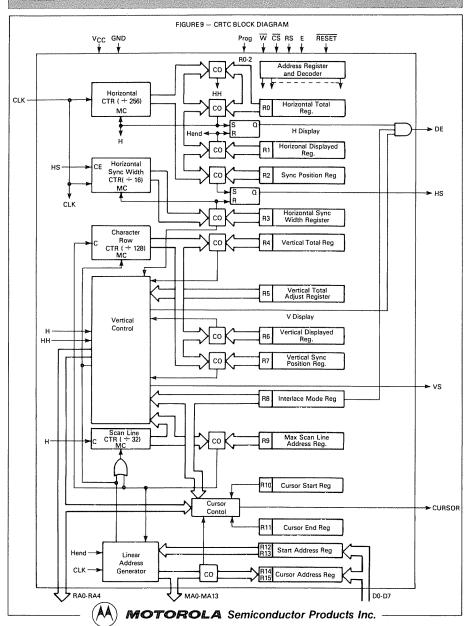

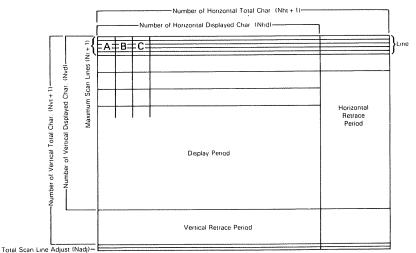

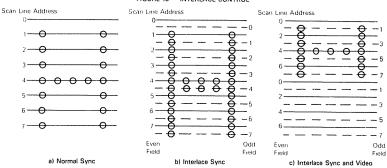

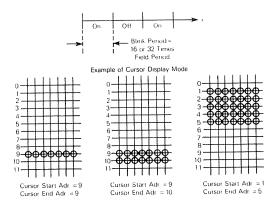

The heart of the video display circuitry in the Model 4 is the 68045 Cathode Ray Tube Controller. The CRTC allows two screen formats: 64 by 16 and 80 by 24. Since the 80 by 24 screen requires 1,920 screen memory locations, a 2K by 8 static RAM is used for the Video RAM. The 64 by 16 mode has a two-page screen display and a bit in the options register for determining which page is active for the CPU. Offset the start address of the CRTC to gain access to the second page in the 64 by 16 mode.

Addresses to the video RAM are provided by the 68045 when refreshing the screen and by the CPU when updating the data. These two sets of addresses are multiplexed by U33, U34, and U35. Data between the CPU and Video RAM is latched by U6 for a write, and buffered by U7 for a read operation.

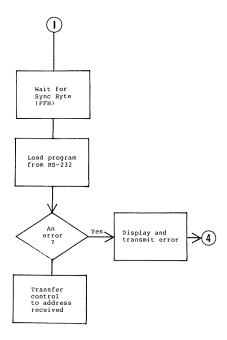

FIGURE 1-2. RAM MEMORY

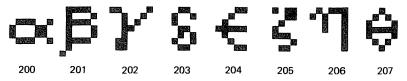

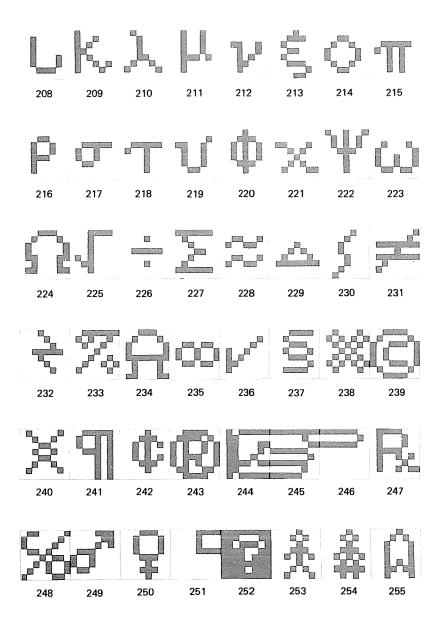

During screen refresh, the data outputs of the Video RAM (ASCII character codes) are latched by U8 and become the addresses for the character generator ROM (U23). In cases of low resolution graphics, a dual 1 of 4 data selector (U9) is the cell generator, with additional buffering from U10

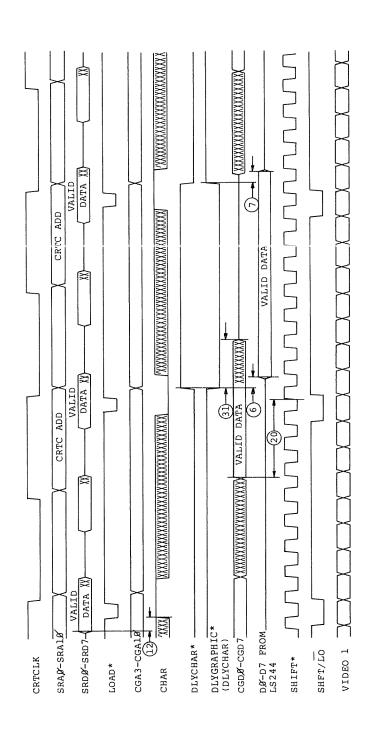

The shift register U11 inputs are the latched data outputs of the character or cell generator. The shift clock input comes from the PAL U4, and is 10.1376 MHz for the 64 by 16 mode and 12.672 MHz for 80 by 24 operation. The serial output from the shift register later becomes actual video dot information.

Special timing in the video circuit is handled by hex latch U2. This includes blanking (originating from CRTC) and shift register loading (originating from U4). Additional video control and timing functions, such as sync buffering, inversion selection, dot clock chopping, and graphics disable of normal video, are handled by miscellaneous gates in U12, U13, U14, U22, U24, and U26.

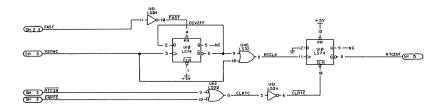

### 1.1.9 Real Time Clock

The Real Time Clock circuit in the Model 4 provides a 30 Hz (in the 2 MHz CPU Mode) or 60 Hz (in the 4 MHz CPU Mode) or 60 Hz (in the 4 MHz CPU Mode) interrupt to the CPU. By counting the number of interrupts that have occured, the CPU can keep track of the time. The 60 Hz vertical sync signal from the video circuitry is divided by two (2 MHz Mode) by U53, and the 30 Hz at pin 1 of U51 is used to generate the interrupts. In the 4 MHz mode, signal FAST places a logic low at pin 1 of U51, causing signal VSYNC to trigger the interrupts at the 60 Hz rate. Note that any time interrupts are disabled, the accuracy of the clock suffers.

### 1.1.10 Cassette Circuitry

The cassette write circuitry latches the two LSBs (D0 and D1) for any output to port FF (hex). The outputs of these latches (U27) are then resistor summed to provide three discrete voltage levels (500 Baud only). The firmware toggles the bits to provide an output signal of the desired frequency at the summing node.

There are two types of cassette Read circuits — 500 baud and 1500 baud. The 500 baud circuit is compatible with both Model 1 and III. The input signal is amplified and filtered by Op amps (U43 and U28. Part of U15 then forms a Zero Crossing Detector, the output of which sets the latch U40. A read of Port FF enables buffer U41, which allows the CPU to determine whether the latch has been set, and simultaneously resets the latch. The firmware determines by the timing between settings of the latch whether a logic "one" or "zero" was read in from the tape.

The 1500 baud cassette read circuit is compatible with the Model III cassette system. The incoming signal is compared to a threshold by part of U15. U15's output will then be either high or low and clock about one-half of U39, depending on whether it is a rising edge or a falling edge. If interrupts are enabled, the setting of either latch will generate an interrupt. As in the 500 baud circuit, the firmware decodes the interrupts into the appropriate data.

For any cassette read or write operation, the cassette relay must be closed in order to start the motor of the cassette deck. A write to port EC hex with bit one set will set latch U42, which turns on transistor Q4 and energizes the relay K1. A subsequent write to this port with bit one clear will clear the latch and de-energize the relay.

### 1.1.11 Printer Circuitry

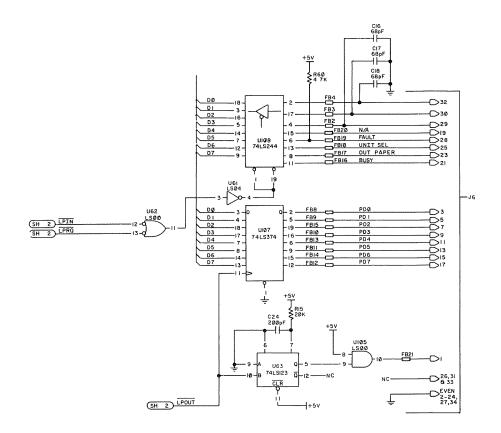

The printer status lines are read by the CPU by enabling buffer U67. This buffer will be enabled for any input from port F8 or F9, or any memory read from location 37E8 or 37E9 when in the Model III mode. For a listing of bit status, refer to the bit map.

After the printer driver software determines that the printer is ready to receive another character (by reading the status), the character to be printed is output to port F8. This latches the character into U66, and simultaneouly fires the one-shot U65 to provide the appropriate strobe to the printer.

### 1.1.12 I/O Connectors

Two 20-pin single inline connectors, J7 and J8, are provided for the connection of a Floppy Disk Controller and an RS-232 Communications Interface, respectively. All eight data lines and the two least significant address lines are routed to these connectors. In addition, connections are provided for device or board selection, interrupt enable, interrupt status read, interrupt acknowledge, RESET, and the CPU WAIT signal.

The graphics connector, J10, contains all of the above interface signals, plus CRTCLK, the dotclock signal, a graphics enable input, and other timing clocks which synchronize the graphics board with the CRTC.

The I/O bus connector, J2, contains connections for all eight data lines (buffered by U74), the low order address lines (buffered by U73), and the control lines (buffered by U75) IN\*, OUT\*, RESET\*, M1\*, and IORQ\*. In addition, the I/O bus connector has inputs to allow the device(s), connected to generate CPU WAIT states and interrupts.

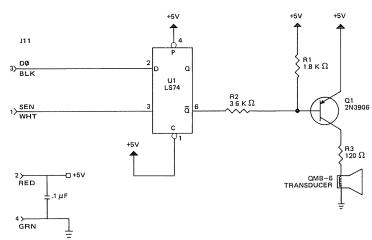

The sound connector, J11, contains only four connections: sound enable (any output to port 90 hex), data bit D0, Vcc, and ground.

### 1.1.13 Sound Option

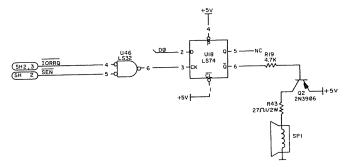

The Model 4 sound option, available as standard equipment on the disk drive versions, is a software intensive device. Data

is sent out to port 90H, alternately setting and clearing data bit D0. The state of this bit is latched by sound board U1 and amplified by sound board Q1, which drives a piezoelectric sound transducer. The speed of the software loop determines the frequency, and thus, the pitch of the resulting tone

### COMPONENT LOCATION/CIRCUIT TRACE, SOUND BOARD #8858121

SCHEMATIC 8000188, SOUND BOARD #8858121

FIGURE 1-4. TIMING OF U4

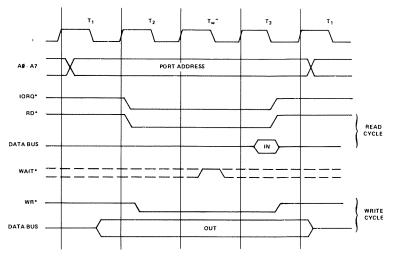

### 1.2 MODEL 4 I/O BUS

The Model 4 Bus is designed to allow easy and convenient interfacing of I/O devices to the Model 4. The I/O Bus supports all the signals necessary to implement a device compatible with the 2-80s I/O structure. That is:

### Addresses:

AØ to A7 allow selection of up to  $256^{\dagger}$  input and 256 output devices if external I/O is enabled.

†Ports 80H to 0FFH are reserved for System use.

### Data

DBØ to DB7 allow transfer of 8-bit data onto the processor data bus if external I/O is enabled.

### Control Lines

- IN\* Z-80 signal specifying that an input is in progress. Gated with IORQ.

- b. OUT\* Z-80 signal specifying that an output is in progress. Gated with IORQ.

- c. RESET\* system reset signal

- d IOBUSINT\* input to the CPU signaling an interrupt from an I/O Bus device if I/O Bus interrupts are enabled.

- IOBUSWAIT\* input to the CPU wait line allowing I/O Bus device to force wait states on the Z-80 if external I/O is enabled.

- f. EXTIOSEL\* input to CPU which switches the I/O Bus data bus transceiver and allows an INPUT instruction to read I/O Bus data.

- g. M1\* and IORQ\* standard Z-80 signals . . . .

The address line, data line, and control lines a to c and e to g are enabled only when the ENEXIO bit in EC is set to a one.

To enable I/O interrupts, the ENIOBUSINT bit in the CPU IOPORT EØ (output port) must be a one. However, even if it is disabled from generating interrupts, the status of the IOBUSINT\* line can still read on the appropriate bit of CPU IOPORT EØ (input port)

See Model 4 Port Bit assignment for port ØFF, ØEC, and ØEØ on pages 14 and 15.

The Model 4 CPU board is fully protected from "foreign I/O devices" in that all the I/O Bus signals are buffered and can be disabled under software control. To attach and use an I/O device on the I/O Bus, certain requirements (both hardware and software) must be met.

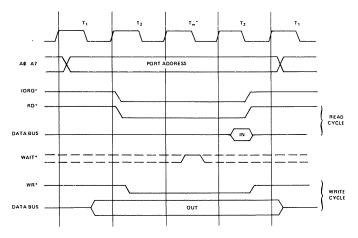

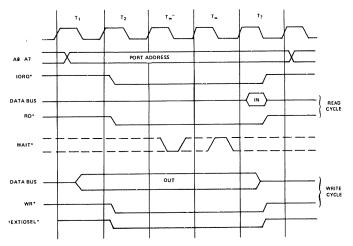

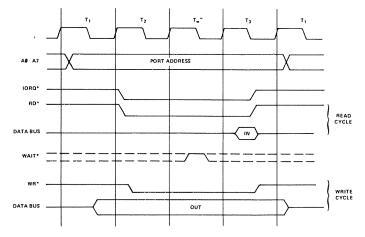

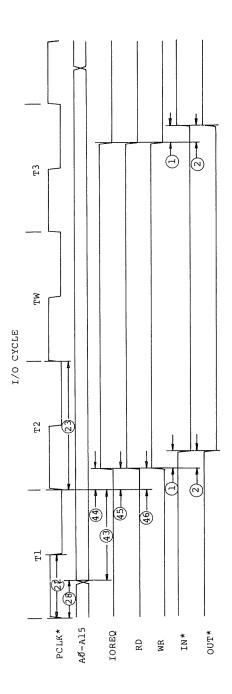

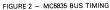

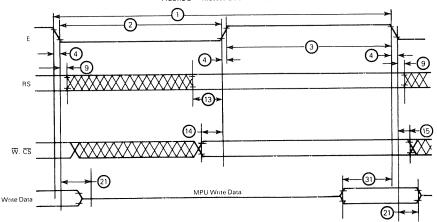

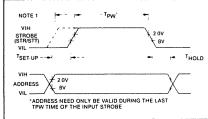

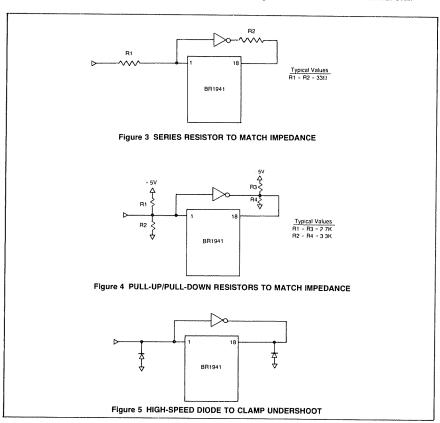

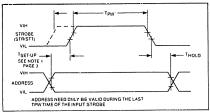

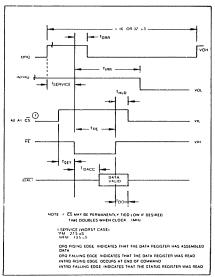

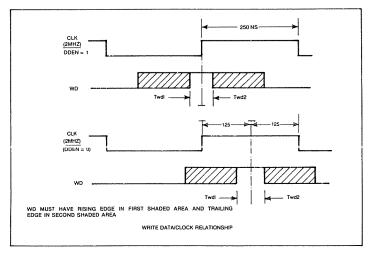

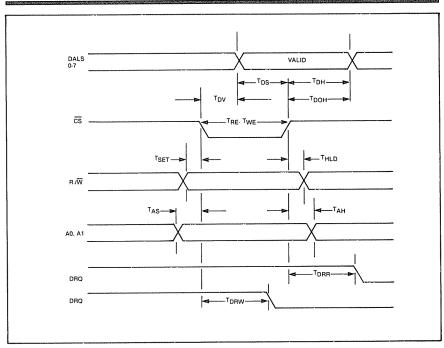

For input port device use, you must enable external I/O devices by writing to port ØECH with bit 4 on in the user software. This will enable the data bus address lines and control signals to the I/O Bus edge connector. When the input device is selected, the hardware will acknowledge by asserting EXTIOSEL\* low. This switches the data bus transceiver and allows the CPU to read the contents of the I/O Bus data lines. See Figure 1.6 for the timing EXTIOSEL\* can be generated by NANDing IN and the I/O port address.

Output port device use is the same as the input port device in use, in that the external I/O devices must be enabled by writing to port ØECH with bit 4 on in the user software — in the same fashion

For either input or output devices, the IOBUSWAIT\* control line can be used in the normal way for synchronizing slow devices to the CPU. Note that since dynamic memories are used in the Model 4, the wait line should be used with caution. Holding the CPU in a wait state for 2 msec or more may cause loss of memory contents since refresh is inhibited during this time. It is recommended that the IOBUSWAIT\* line be held active no more than 500 µsec with a 25% duty cycle

The Model 4 will support Z-80 mode 1 interrupts. A RAM jump table is supported by the LEVEL II BASIC ROMs and the user must supply the address of his interrupt service routine by writing this address to locations 403E and 403F. When an interrupt occurs, the program will be vectored to the user supplied address if I/O Bus interrupts have been enabled. To enable I/O Bus interrupts, the user must set bit 3 of Port 0E0H.

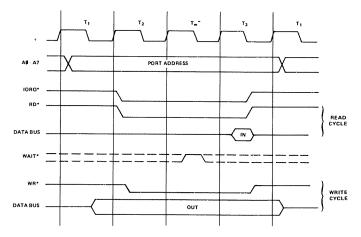

Input or Output Cycles

"Inserted by Z80 CPU

Input or Output Cycles with Wait States.

"Inserted by Z80 CPU

†Coincident with IORO\* only on INPUT cycle

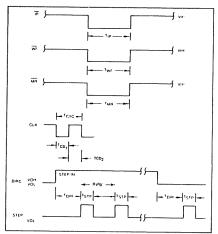

FIGURE 1-6. I/O BUS TIMING DIAGRAM

### 1.3 MODEL 4 PORT BITS

Name: WRNMIMASKREG

Port Address: ØE4H

Access: WRITE ONLY

Bit 7 = ENINTRQ; Ø disables Disk INTRQ from generating

an NMI

1 enables above

Bit 6 = ENDRQ; Ø disables Disk DRQ from generating an

NMI

1 enables above

Name: RDNMISTATUS\*

Port Address: ØE4H Access: READ

READ ONLY

Bit 7 = Status of Disk INTRQ;  $1 = False_0 = True$

Bit 6 = Status of Disk DRQ; 1 = False Ø = True

Bit 5 = Reset \* Status: 1 = False, Ø = True

Name: MOD OUT Port Address: ØECH

Access: WRITE ONLY

Bit 7 = Undefined

Bit 6 = Undefined

Bit 5 = DISWAIT; Ø disables video waits, 1 enables

Bit 4 = ENEXTIO; Ø disables external IO Bus, 1 enables

Bit 3 = ENALTSET; Ø disables alternate character set.

1 enables alternate video character set

Bit 2 = MODSEL; Ø enables 64 character mode,

1 enables 32 character mode

Bit 1 = CASMOTORON; Ø turns cassette motor off.

1 turns cassette motor on

Bit Ø = Undefined

Name: RDINTSTATUS\*

Port Address: ØEØH

Access: READ ONLY

NOTE: A Ø indicates the device is interrupting

Bit 7 = Undefined

Bit 6 = RS-232 ERROR INT

Bit 5 = RS-232 RCV INT

Bit 4 = RS-232 XMIT INT

Bit 3 = IOBUS INT

Bit 2 = RTC INT

Bit 1 = CASSETTE (1500 Baud) INT F

Bit Ø = CASSETTE (1500 Baud) INT R

Name: CASOUT\*

Port Address: ØFFH

Access: WRITE ONLY

Bit 7 = Undefined

Bit 6 = Undefined

Bit 5 = Undefined

Bit 4 = Undefined

Bit 3 = Undfined

Bit 2 = Undefined

Bit 1 = Cassette output level

Bit Ø = Cassette output level

Name: WRINTMASKREG\*

Port Address: ØEØH Access: WRITE ONLY

Bit 7 = Undefined

Bit 6 = ENERRORINT; 1 enables RS-232 interrupts on parity error, framing error, or data overrun error

Ø disable above

Bit 5 = ENRCVINT; 1 enables RS-232 receive data register

full interrupts.

Ø disables above

Bit 4 ≈ ENXMITINT; 1 enables RS-232 transmitter holding register empty interrupts.

Ø disables above

Bit 3 = ENIOBUSINT; 1 enables I/O Bus interrupts,

Ø disables the above

Bit 2 = ENRTC; 1 enables real time clock interrupt,

Ø disables above.

Bit 1 = ENCASINTF: 1 enables 1500 Baud falling edge inter-

rupt.

Ø disables above

Bit  $\emptyset$  = ENCASINTR; 1 enables 1500 Baud rising edge inter-

rupt,

Ø disables above

Name: CAS IN\*

Port Address: ØFFH

Access: READ ONLY

Bit 7 = 500 Baud Cassette bit

Bit 6 = Undefined

Bit 5 = DISWAIT (See Port ØECH definition)

Bit 4 = ENEXTIO (See Port ØECH definition)

Bit 3 = ENALTSET (See Port ØECH definition)

Bit 2 = MODSEL (See Port ØECH definition)

Bit 1 = CASMOTORON (See Port ØECH definition)

Bit Ø = 1500 Baud Cassette bit

NOTE: Reading Port ØFFH clears the 1500 Baud Cassette interrupts

Name: DRVSEL\* Port Address: 0F4H

Access: WRITE ONLY

Bit 7 = FM\*/MFM; Ø selects single density, 1 selects double density

Bit 6 = WSGEN: Ø = no wait states generated, 1 = wait states generated

Bit 5 = PRECOMP; Ø = no write precompensation. 1 = write precompensation enabled.

Bit 4 = SDSEL; Ø selects side Ø of diskette.

1 selects side 1 of diskette

Bit 3 = Drive select 4

Bit 2 = Drive select 3

Bit 1 = Drive select 2

Bit Ø = Drive select 1

### SECTION II 4 GATE ARRAY THEORY OF OPERATION

### 2.1 MODEL 4 GATE ARRAY THEORY OF OPERATION

### 2.1.1 Introduction

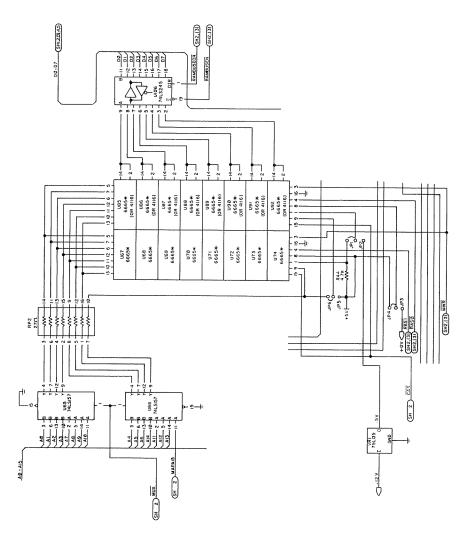

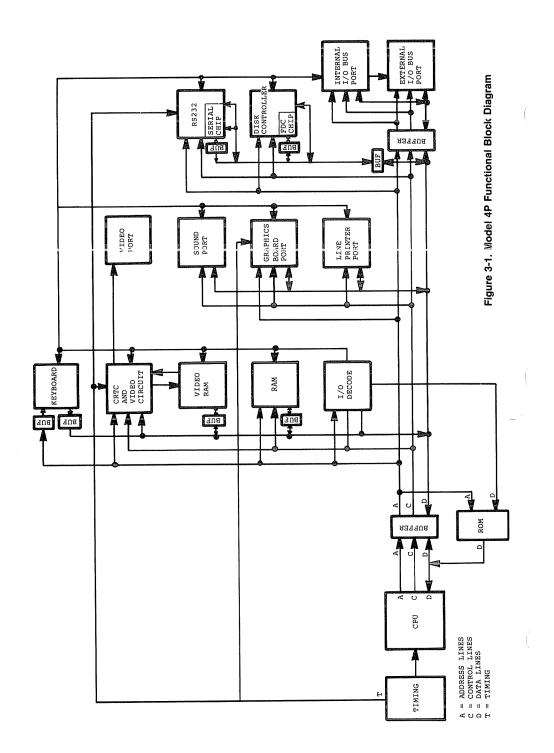

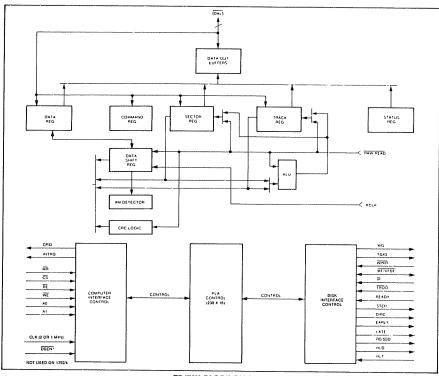

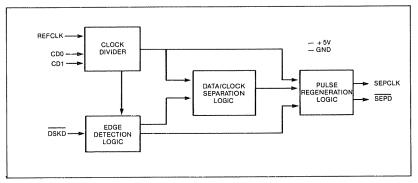

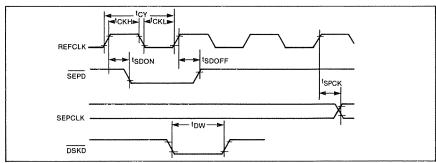

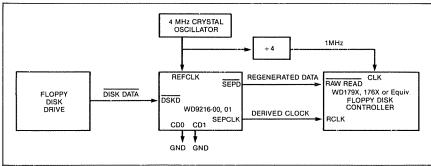

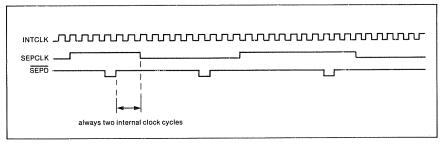

The following discusses each element of the main board of the Model 4 Gate Array block diagram (see Figure 2-1). In each case the intent is understanding the operation on a practical level sufficient to aid in isolating a problem to the failing component.

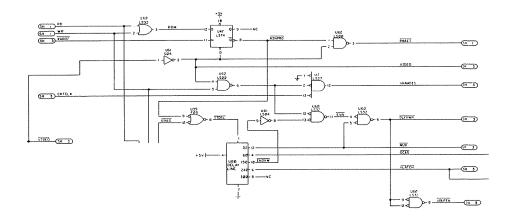

### 2.1.2 Reset Circuit

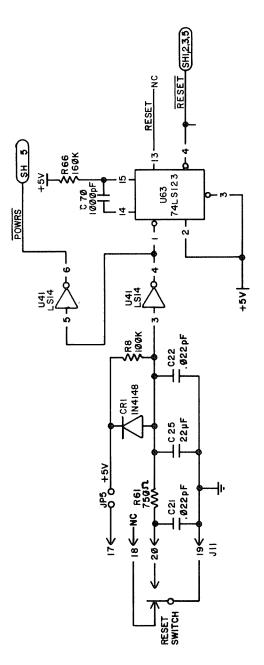

Figure 2-2 shows the Reset circuit for generation of reset on power up and when the reset switch is pushed on the key-board. The time constant determined by R8 and C25, is used to allow the system to stabilize before triggering a one shot (U63) with an approximate pulse width of 70 microsecs. When the reset switch is pushed, the input pin is brought to ground and fires the one shot when the switch is released.

A second point to be noted is the signal POWRS\* which is used to reset the drive select latch in the FDC circuit

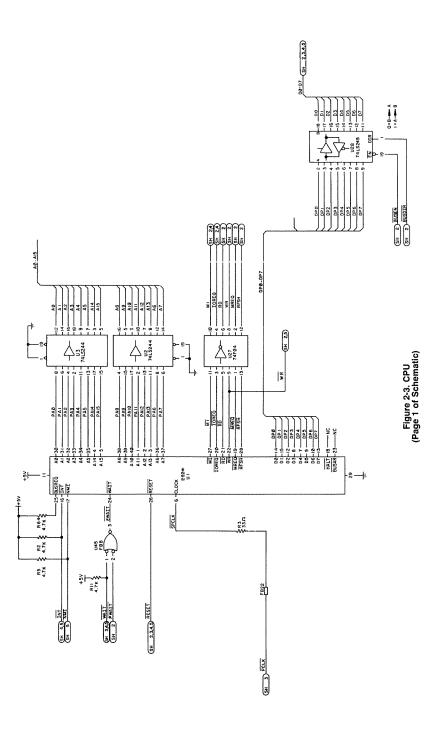

### 2.1.3 CPU

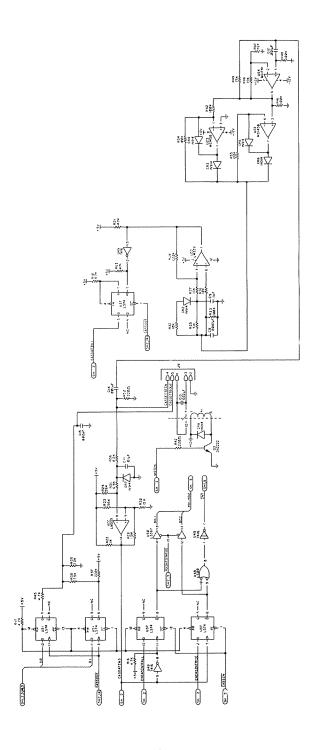

The central processing unit of the Model 4 microcomputer is a Z80A microprocessor, and will run in either 2 or 4 MHz mode. All of the output lines of the Z80A are buffered. The address lines are buffered by two 74LS2445 (UZ and U3 with the enable tied to ground), the control lines by a 74F04 (UZ7), and the data lines by a 74LS245 (U28 with the enable tied to BUSEN\* and the direction control tied to BUSEIN\*).

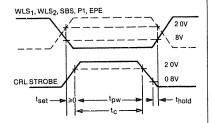

### 2.1.4 System Timing and Control Registers

### **Control Registers**

The first of these registers is the WRINTMASKREG (U34) This is only part of the register as this function is shared with the Gate Array 4.5. The main register contains RTC ENCASINTFALL AND ENCASINTRISE. The Gate Array has the interrupts for the RS232C Interface and the I/O bus interrupts and a duplicate of the RTC

The second is the OPREG (U33) which contains the added options of the Model 4 for video and Memory mapping

The last of the registers is MODOUT (U53) and is also readable through the CASSIN (U52) buffer. It contains the Cassette motion controls, and the FAST control for Model 4

### CPU Clock and RS232 Clock

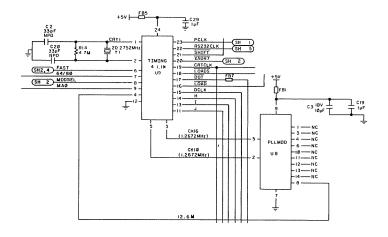

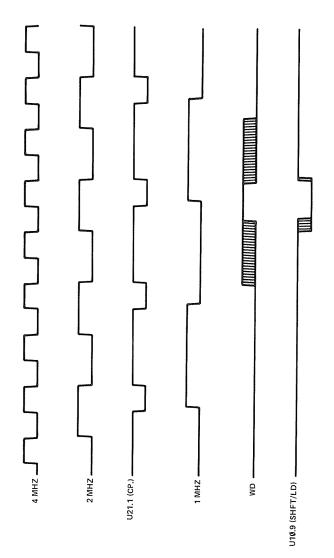

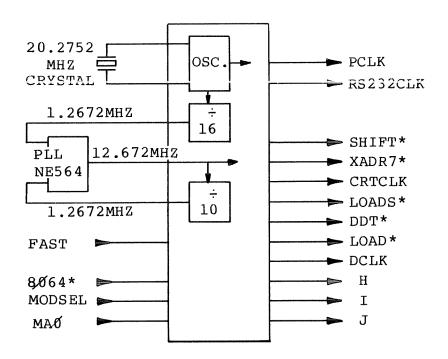

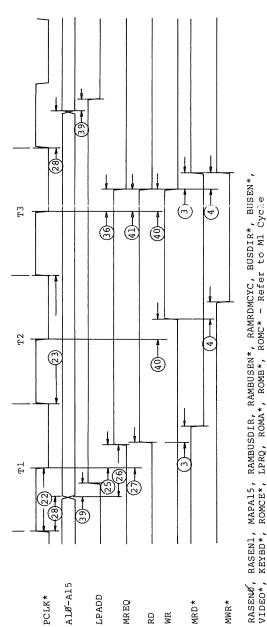

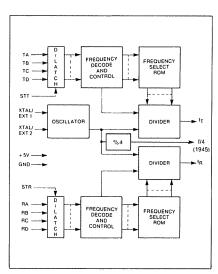

Most of the timing generation for the board is shown in Figure 2-5. The Gate Array 4.1.1 is the basis for this timing as it produces the 20.2752 MHz clock and then divides this down to produce most of the other clocking functions used on the board

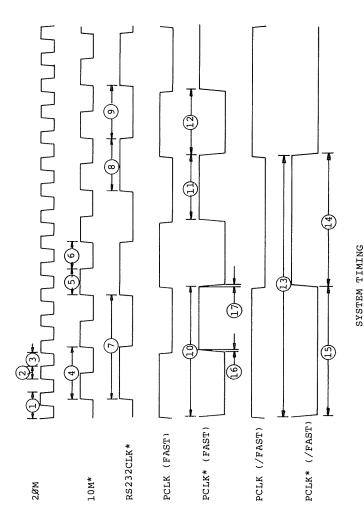

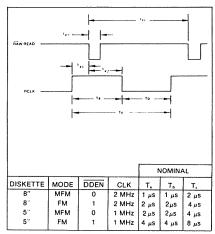

The first clock that is produced is PCLK (pin 23) which drives the CPU. It is a divide by ten of the 20.2752 MHz in the 2 MHz mode and a divide by 5 in the 4 MHz mode. The transition from one mode to the other is without glitches and both modes are 50 percent duty cycles

Note that the signal that controls this mode also controls the Real Time Clock circuit described later.

As a simple divide by four of the fundamental 20 2752 MHz, the RS232CLK on pin 22 of U9 provides the basic clock to the RS232C circuit

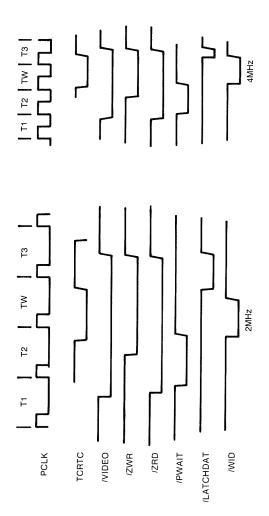

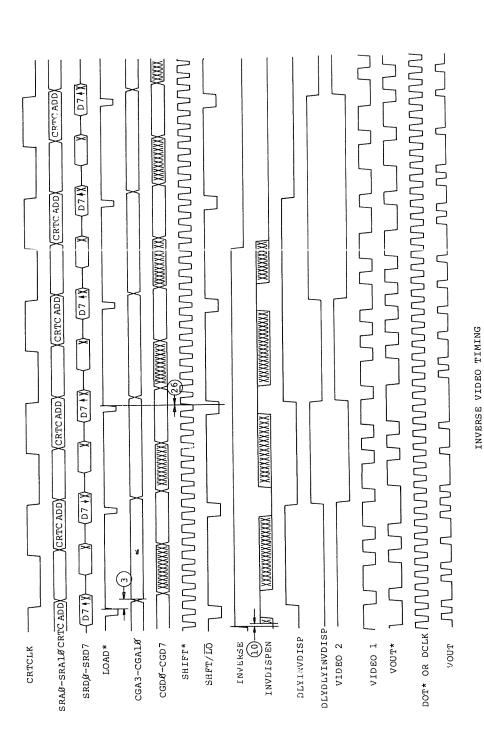

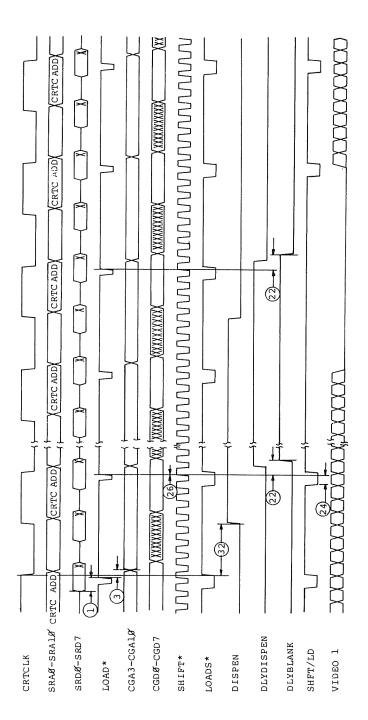

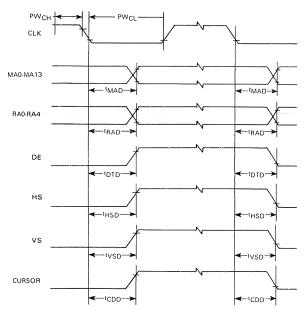

### Video and Graphics Clocking and Timing

The timing for both of these functions may be viewed as one since they must operate synchronously and the same timing must be generated for both. The additional signals sent to the Graphics Board allow it to maintain synchronization by knowing the phase relation of the signals sent to both of them. To further understand the circuit of Figure 2-5 notice the PLL Module (U8). This chip develops a 12 672 MHz signal which is phase locked to the 1 2672 MHz input on pin 5 and is a divide by 16 of the primary 20 2752 MHz clock This provides the Gate Array 4.1 1 with two clocks to drive the video display and the graphics circuits, 10 1376 MHz for 64 character display, and a 12 672 MHz for the 80 character display.

The following discussion will consider both the 64 and 80 character displays to be the same, the difference being the primary frequency and not the phase relation or function of the signals generated.

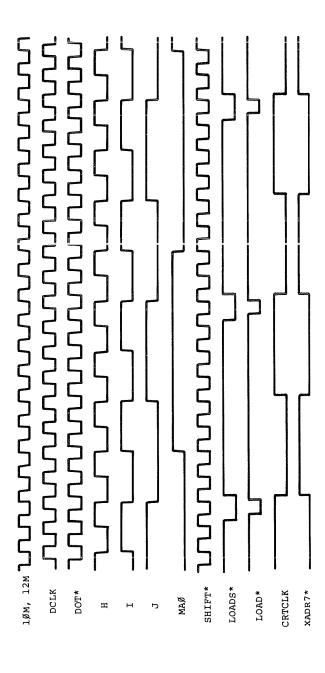

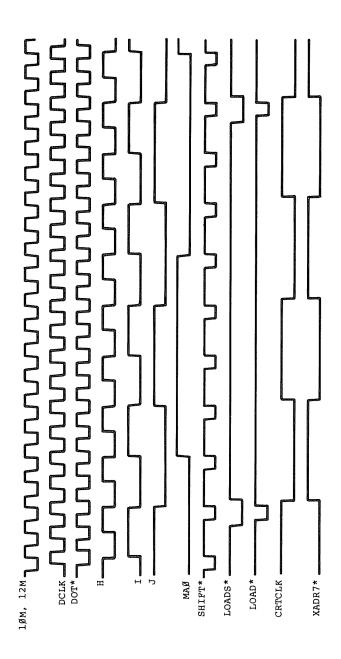

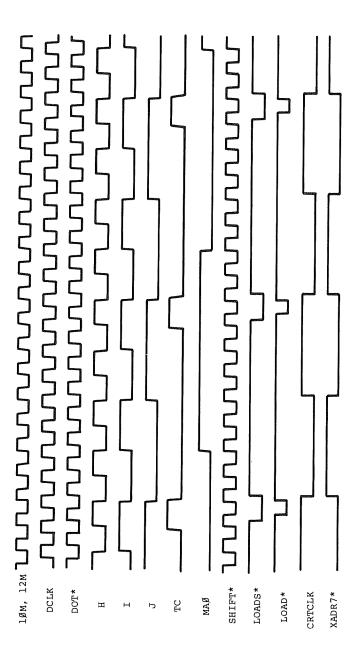

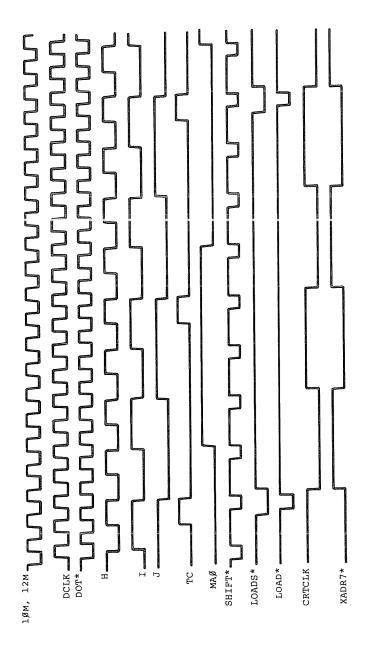

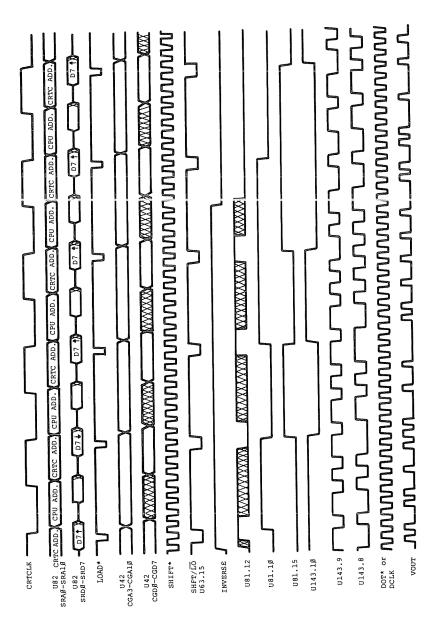

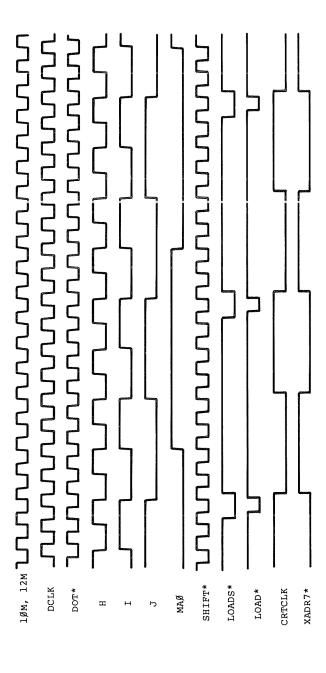

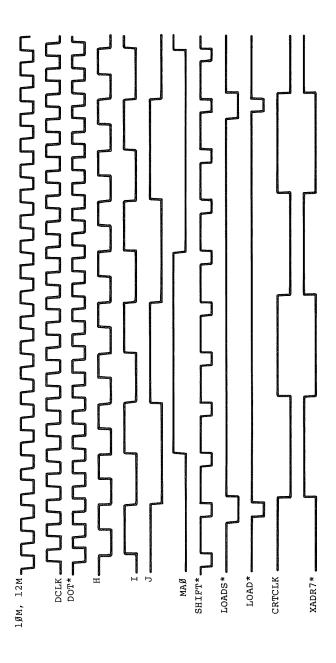

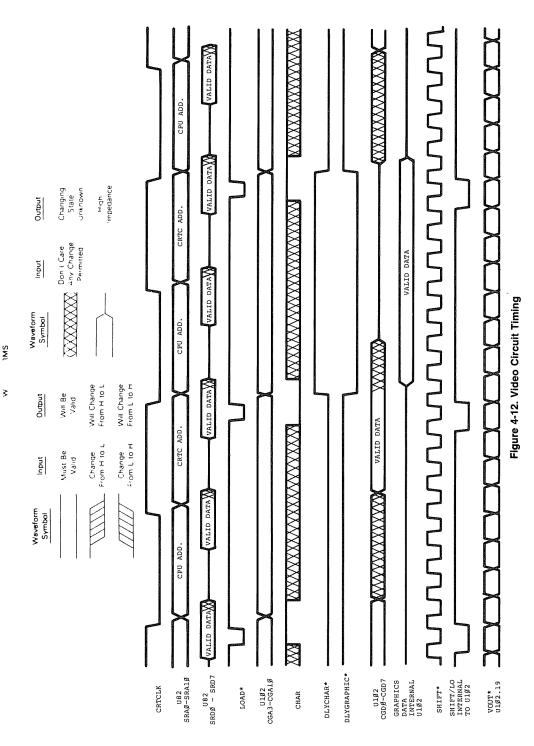

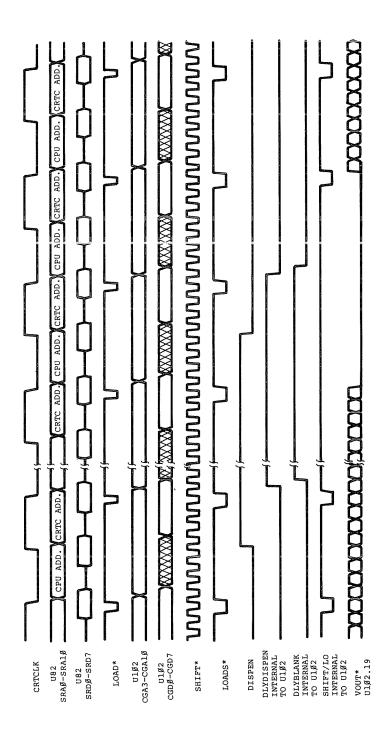

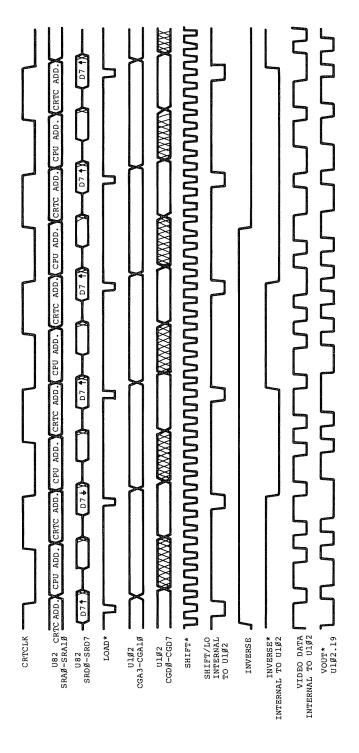

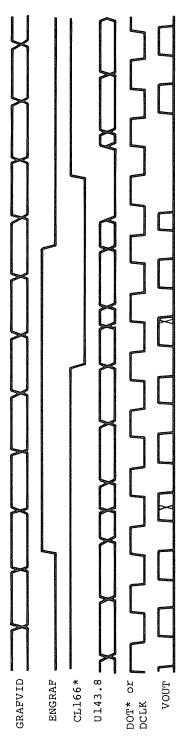

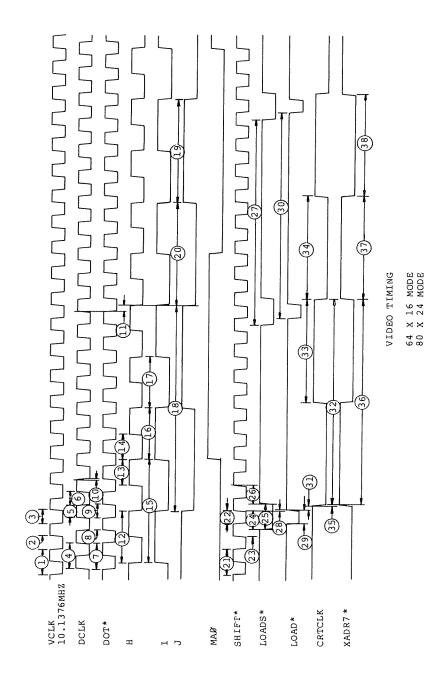

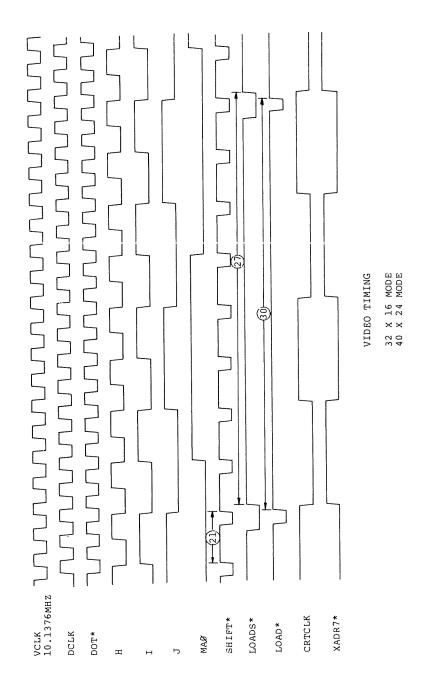

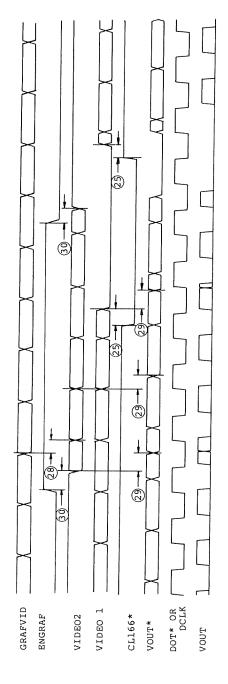

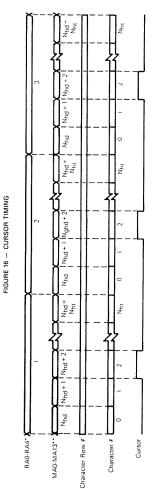

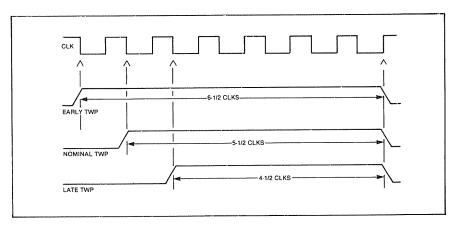

The reference clock for the timing is DCLK (U9-15) and the other clocks that are produced for the video output are derived from this clock (DOT\* at U9-17 is a phase shift of DCLK and is provided as an option for the the dot clock for variations in delay paths in the video section) U9 then generates SHIFT\* (pin 21), XADR7\* (pin 20), CRTCLK (pin 19), LOADS\* (pin 18), and LOAD\* (pin 16) for the proper timing for the four video modes in addition for the Graphics Board to synchronize with this timing H (pin 14), I (pin 13), and J (pin 11) are fed to connector J12 See Figures 2-6 and 2-7 for the timing diagrams for video clocks generated by Gate Array 4.1.1

Figure 2-2. Reset Circuit (Page 4 of Schematic)

Figure 2-4. Control Registers (Page 2 of Schematic)

Figure 2-5. CPU, RS232C, and Video Timing Generation (Page 3 of Schematic)

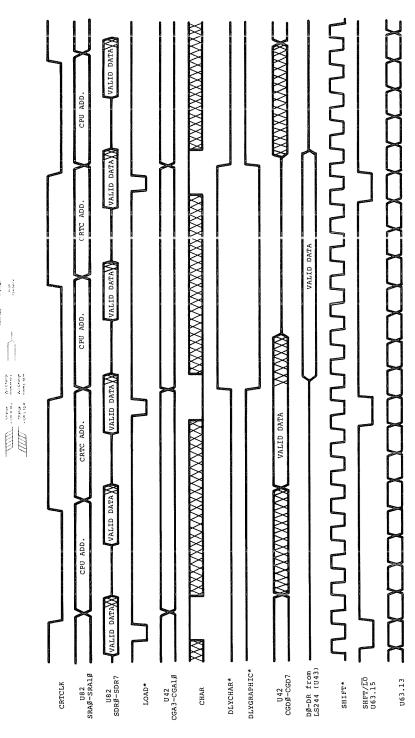

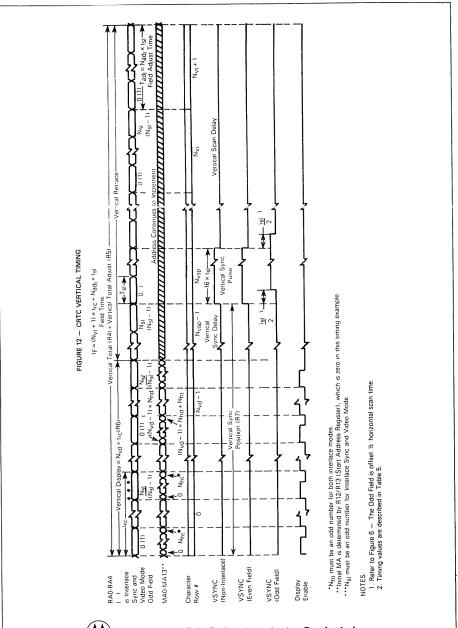

Figure 2-6. Video Timing 64 x 16 Mode 80 x 24 Mode

### **DRAM and Video RAM Timing**

The Video RAM and DRAM timing share the timing delay line (U80) This is done by "OR"ing the two signals GRAS\*, and AINPRG\* at U39 to get the signal STDEL\* This is possible because the signals VIDEO and MREQ or MCYCEN are gated in to mask off the signals that are not desired

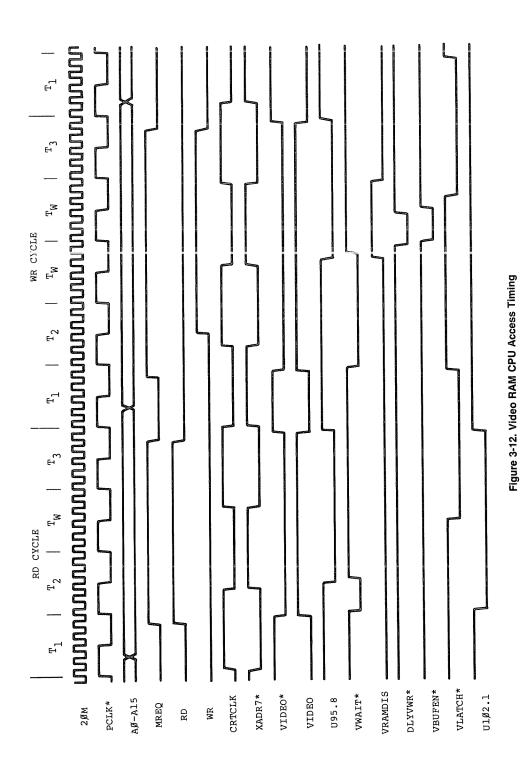

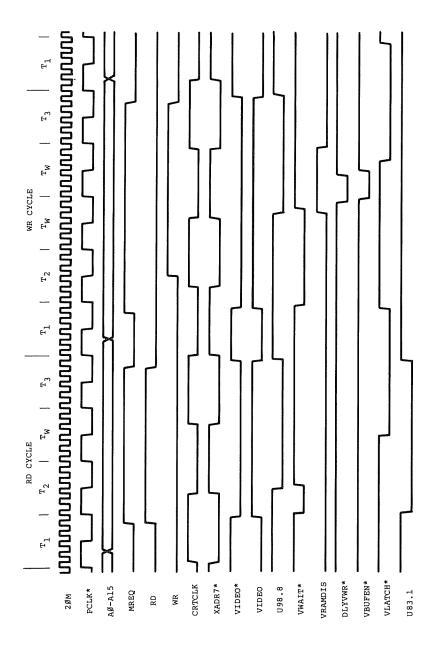

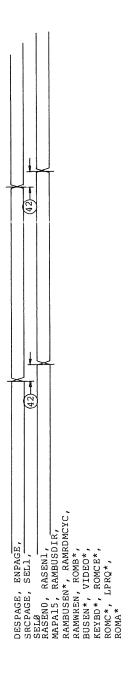

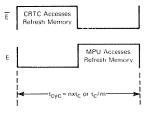

Since the CRTC and the CPU are operating independently and at different clock rates, when the CPU wants to access the Video RAM the two must synchronize with each other This is accomplished when a video access is decoded WAIT\* It is pulled low, when it is determined whether the access is a read or write and the correct cycle of the CRTC clock is present, the actual access can begin, hence AINPRG\* is generated and WAIT\* is released

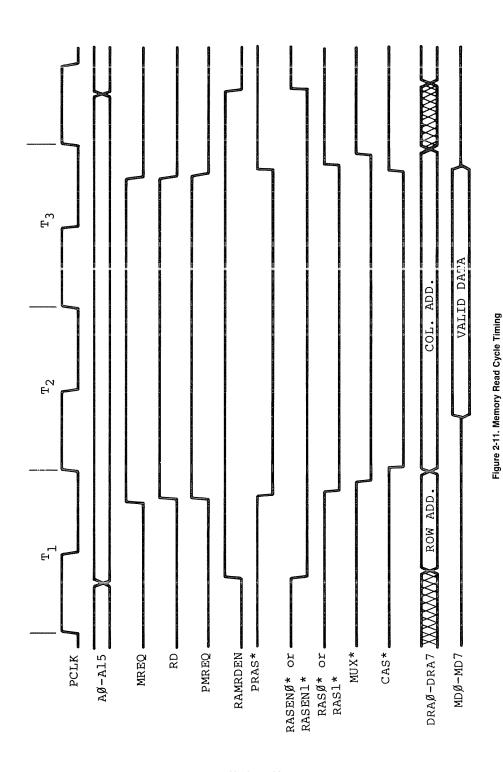

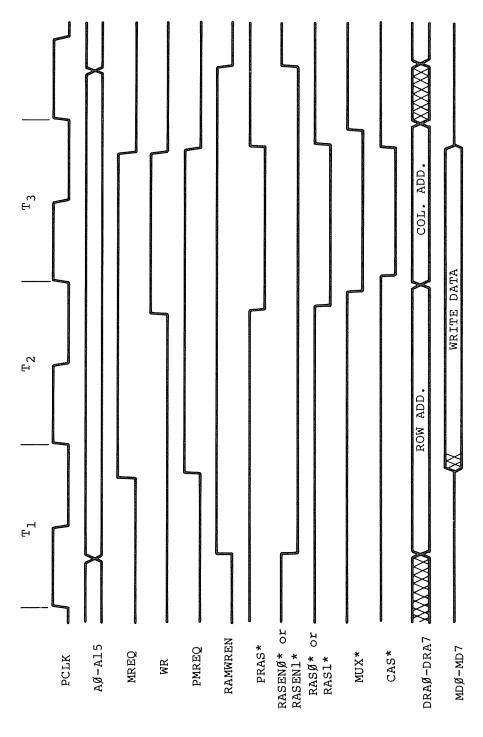

From this point the actual sequence depends on whether a read or a write is done. On a read the address is enabled to the RAM, the delay through U80 to VLATCH\* when data is latched in the 74LS373 where the CPU can pick-up the data at the completion of this cycle. On a write the sequence is more complex. The address is enabled to the RAM, the output is disabled (VRAMDIS\* at U7-12), write is delayed with respect to the address (DLYWR\* at U80-6) and the buffer on the data lines is enabled (VBUFEN\* at U60-8), then after a delay the write is cutoff to end the cycle for the RAM (ENDVW\* at U80-10). For the timing diagram of the Video RAM CPU access see Figure 2-8.

### **DRAM Timing**

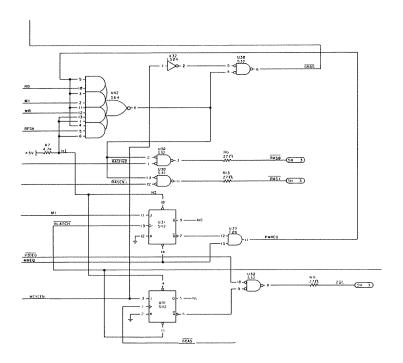

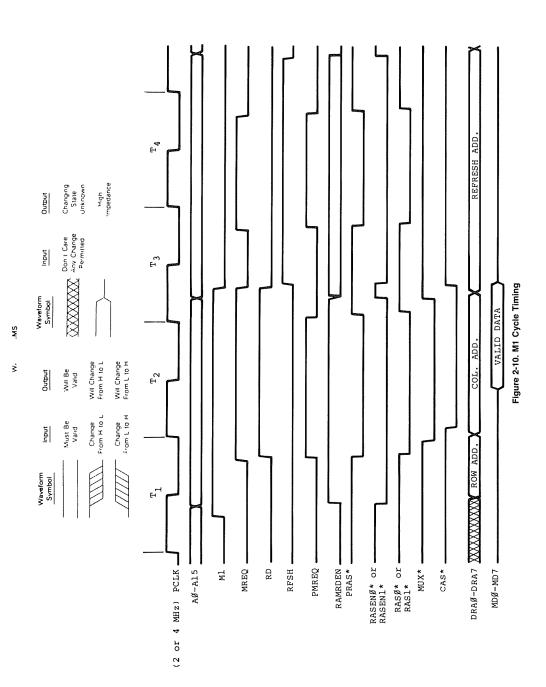

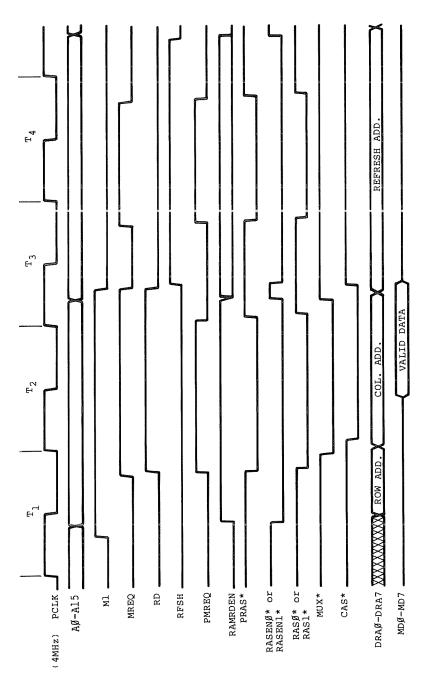

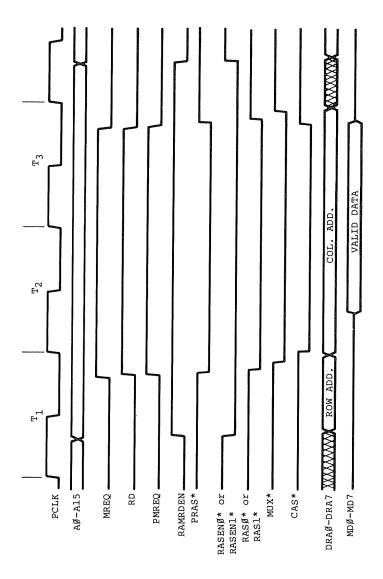

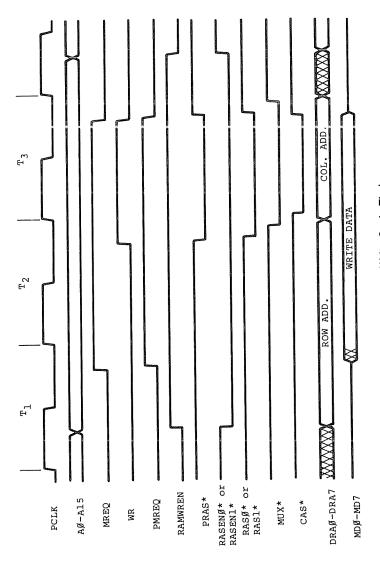

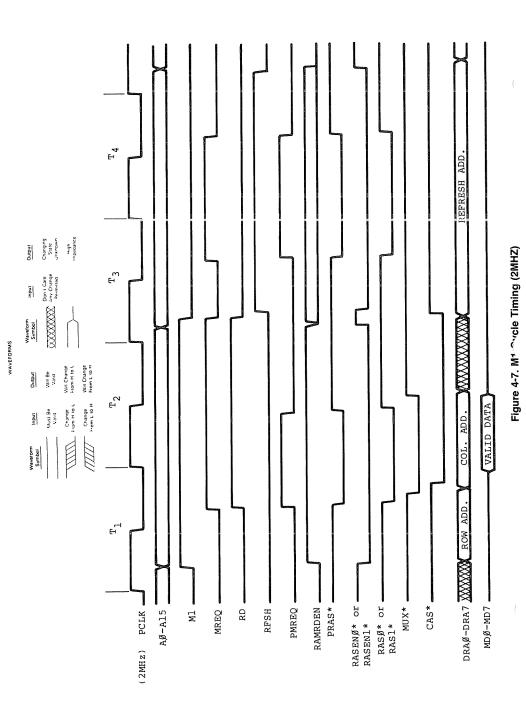

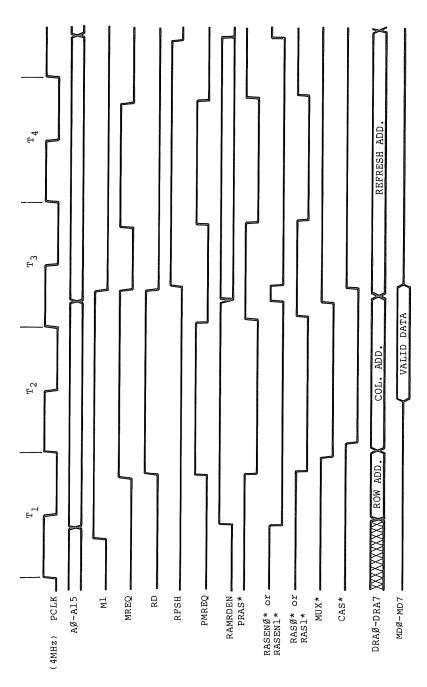

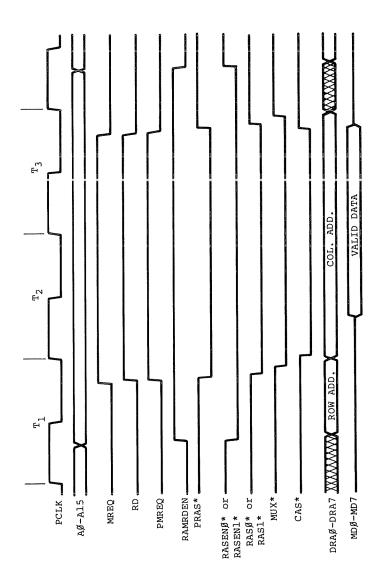

The DRAM timing is shown in Figure 2-9 At the begining of the CPU cycle the address lines settle-out first and are. therefore, decoded to allow maximum access speed (see Address Decode). With the generation of MREQ, U39-11 generates PMREQ and enables U42 and gates this with the type of cycle to develop GRAS\* (U30-6), RASO\* (U30-3), and RAS1\* (U30-11). GRAS\* is then "OR"ed with AINPRG as mentioned above. The timing from this point is very straight forward. With RASO\* and RAS1\* generated next MUX (U80-12) is built to switch the addresses to memory then GCAS is generated and clocks flip-flop U31 with MCYEN on the J term. This is done to make sure this is a true memory cycle. Then if this is an M1 cycle VLATCH\* clocks at U31 and cuts off PMREQ\* at U39 to end the cycle. For timing diagrams of the memory interface see Figures 2-10 to 2-12

### 2.1.5. Address Decode

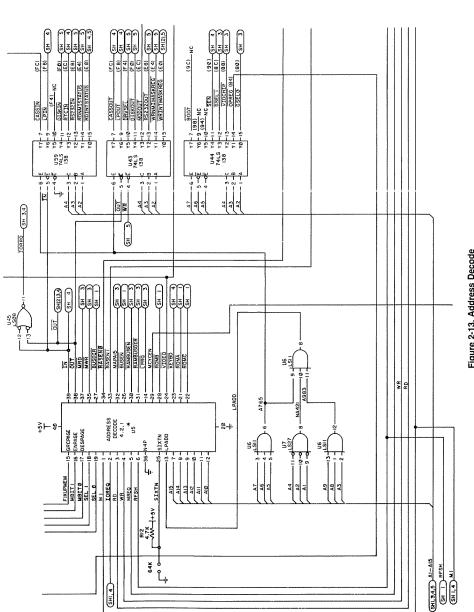

This section is divided into two parts, the memory addressing and the I/O addressing. This separation is a reflection of the separate mapping of memory and I/O of the Z8OA itself. For reference of both sections, see Figure 2-13.

### **Memory Address**

The memory map for the Model 4 is shown in Table 2-1 and is best described as an option overlay in the sense that at each step of additional memory, the new options overlap the previous and the new options are added on Moreover, the added options have no effect on previous levels and are invisible at those levels

|                                     | Address in hex           |                        |           | Function               |

|-------------------------------------|--------------------------|------------------------|-----------|------------------------|

| MAP I*                              | MAP II                   | MAP III                | MAP IV    | of block               |

| 2000 0757                           | 0000-37FF                | 0000-F3FF              | 0000-FFFF | RAM (64K)<br>ROM       |

| 0000-37E7<br>37E8-37E9<br>37EA-37FF |                          |                        |           | Printer Status<br>ROM  |

| 3800-3BFF<br>3C00-3FFF**            | 3800-3BFF<br>3C00-3FFF** | F400-F7FF<br>F800-FFFF |           | Keyboard<br>Video RAM  |

| 4000-7FFF<br>4000-FFFF              | 4000-FFFF                |                        |           | RAM (16K)<br>RAM (64K) |

### Table 2-1

The decoding of the addresses for the memory map described above is done for the most part by U5. The only decode not done by U5 is the line printer memory status port at 37E8 and 37E9 hex. These needed additional address lines hence the decode LPADD as an input to U5.

<sup>\*</sup> Only map available on 16K machine

<sup>\*\*</sup> Page bit is used to select 1K of 2K Video RAM

Figure 2-8. Video RAM CPU Access Timing

Figure 2-9. Video RAM and DRAM Timing Circuit.

(Page 2 of Schematic)

Hardware 32

Figure 2-12. Memory Write Cycle Timing

Hardware 33

Figure 2-13. Address Decode (Page 2 of Schematic)

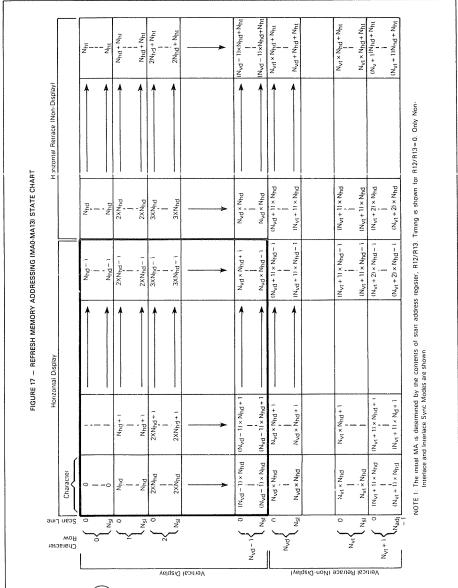

Table 2-2. RAM Memory

### I/O port Address

The Port Map decoding is accomplished by three 74LS138s (U43,U44, and U59). These ICs decode the low order adress lines (A0 – A7) from the CPU and decode the port being selected. The IN\* signal and OUT\* signal are used in the decode for U59 and U43, but U44 is a pure address decode and, therefore, needs to be gated with IN\*, OUT\*, or IOREO\* later. For a complete I/O map see Table 2-3.

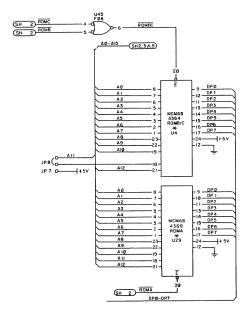

### 2.1.6. ROM

The A ROM is enabled by the decode as appropriate by the address logic described above, and is addressed in a simple straight forward fashion. The enable for the B/C ROM is also similarly accomplished, however, the address has a jumper option available This option is designed to allow for testing of the board logic in the factory When jumper is moved from JP8 to JP7, the ROM is in the test mode, with the options appearing on the screen.

### 2.1.7 DRAW

The DRAM timing was described earlier in the timing section, the actual DRAM is contained in two banks of eight each U65 to U74 and U85 to U92. They are arranged in order of data bits D0 through D7, U65 and U85 being D0, through U74 and U92 being D7. Note in Figure 2-15 that the two banks are different with jumper options in the lower bank, these options are for the possible use of 16k three voltage parts When jumpered as shown in Figure 2-14 the bank is identical to the second bank and is for using 64k DRAMs With both banks filled there is 128k available to the

### 2.1.8 Video Circuit

### Video Modes

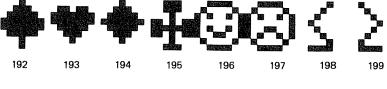

The Model 4 has many video options available through hardware and software. Software has control of inverse video on a character by character basis by turning on IN-VIDE. Note that this implies the available number of characters is now 128 since the most significant bit of the character code in memory is now used to indicate inverse character. Similarly, an alternate character set can be enabled by turning on ENALTSET. This enables a new 64 characters in place of the last 64 characters, that is, the Kana set in place of the game set. An option not available to software is an enhanced character, which moves characters down one row in their character block to make an inverse character appear within the inverse block and not on the edge of the block. This is done by moving jumper JP11 to JP12. As an example of a combination of hardware and software options available in the video is the overlay, which not only requires the Graphics Board to be installed, but also software to enable the graphics data and the video data with text at the same time

The Model 4 also has an option for either 64 character or 80 character wide screen. The 64 character screen is compatible with the Model III and displays 16 lines. The 80 character screen displays 24 lines. In addition each of these has a double width mode. These options are controlled by two bits, MODSEL and 8064 which provide the screens as shown in the following table.

| 8064 | MODSEL | Video Screen Size |

|------|--------|-------------------|

| 0    | 0      | 64 x 16           |

| Ō    | 1      | 32 x 16           |

| 1    | Ó      | 80 x 24           |

| 1    | ī      | 40 x 24           |

Table 2-4

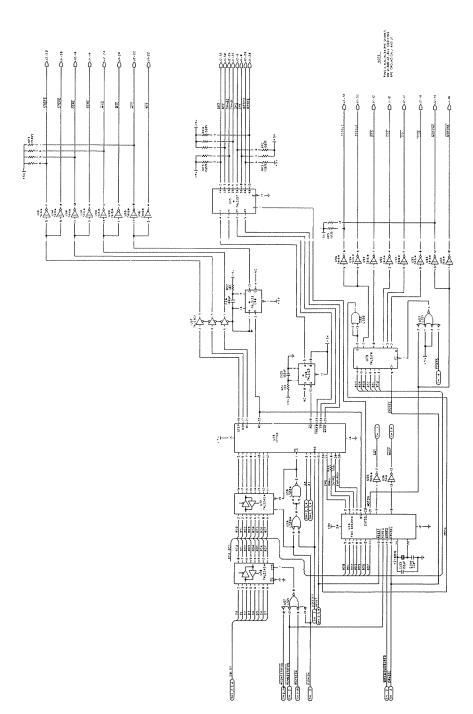

With this information of the options available to the user we can now view the actual operation of the circuit with the final objectives in mind and see how they are achieved. For the rest of this section all references will be made to Figure 2-16. The first task to be accomplished would be the screen refresh and this is done by the CRTC or 68045 (U11) which will generate the addresses continuously on its address lines. Then to allow the CPU access to the same memory the address lines are multiplexed at U12, U14, and U15 on opposite phases of the CRT clock. The CPUs access timing is then handed by the timing circuit described earlier.

The data bus of the RAM (U16) is a two way bus with the RAM as a source or destination on all accesses, the video gate array (U17) is the destination on the screen refresh half of the cycle, the 74LS373 (U36) is the destination on a read of the RAM by the CPU, and the 74LS244 (U35) is the source on writes to the RAM.

The video gate array then gates the RAM data INVIDE, and ENALTSET to determine the ROM addressing for these two options and CHRADD to the 74LS283 (U13) which takes the row address from the 68045 and adds a zero to the row address or a minus one to form the character enhanced mode.

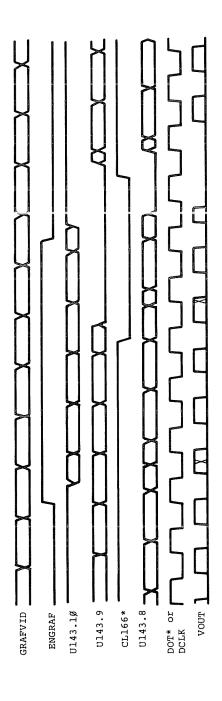

The data out of the ROM is then sent back to the gate array where it is then changed to a serial stream of data which is synchronized with the data that would come from the graphics board, GRAFVID. The signal CL166 will inhibit the data out of the serial register and the signal ENGRAF enables the graphics data, hence, if both are enabled the effect is an overlay. The output data is sent to U20 pin 9 where it is gated with one of two phases of the dot clock; then after being filtered to lower the R.F.I. it is output to the sweep board.

### Model 4 Port Bit Map

| Port               | D7             | D6                | D5                 | D4                 | D3               | D2               | D1               | D0               |

|--------------------|----------------|-------------------|--------------------|--------------------|------------------|------------------|------------------|------------------|

| FC · FF            | Cass           |                   |                    |                    |                  |                  |                  | Cassette         |

| (READ)             | data<br>500 bd |                   | (MIF               | RROR of P          | ORT EC)          |                  |                  | data<br>1500 bd  |

| FC-FF              |                | (1)               | lote, also resets  | cassette data l    | atch)            |                  | cass.            | cassette         |

| (WRITE)            | ×              | ×                 | ×                  | x                  | ×                | ×                | out              | data out         |

| F8 - FB<br>(READ)  | Prntr<br>BUSY  | Prntr<br>Paper    | Prntr<br>Select    | Prntr<br>Fault     | x<br>x           | x<br>x           | x<br>x           | x<br>x           |

| F8 - FB<br>(WRITE) | Prntr<br>D7    | Prntr<br>D6       | Prntr<br>D5        | Prntr<br>D4        | Prntr<br>D3      | Prntr<br>D2      | Prntr<br>D1      | Prntr<br>D0      |

| EC-EF              |                |                   | (Any Read          | causes reset of    | Real Time Cloc   | k Interrupt)     |                  |                  |

| EC - EF<br>(WRITE) | x<br>x         | CPU<br>Fast       | x<br>x             | Enable<br>EX I/O   | Enable<br>Altset | Mode<br>Select   | Cass<br>Mot On   | x<br>x           |

| E0 - E3<br>(READ)  | x<br>x         | Receive<br>Error  | Receive<br>Data    | Xmit<br>Empty      | 10 Bus<br>Int    | RTC<br>Int       | C Fall<br>Int    | C Rise<br>Int    |

| E0 · E3<br>(WRITE) | x<br>x         | Enable<br>Rec Err | Enable<br>Rec Data | Enable<br>Xmit Emp | Enable<br>10 Int | Enable<br>RT Int | Enable<br>CF Int | Enable<br>CR Int |

| 90 - 93<br>(WRITE) | x<br>x         | x<br>x            | x<br>x             | x<br>x             | x<br>x           | x<br>x           | x<br>x           | Sound<br>Bit     |

| 84 - 87<br>(WRITE) | Page           | Fix Upr<br>Memory | Memory<br>Bit 1    | Memory<br>Bit 0    | Invert<br>Video  | 80/64            | Select<br>Bit 1  | Select<br>Bit 0  |

Table 2-3. I/O Port Map

Figure 2-14. ROM Circuit (Page 1 of Schematic)

Figure 2-15. DRAM Circuit (Page 3 of Schematic)

Figure 2-16. Video Circuit (Page 3 of Schematic)

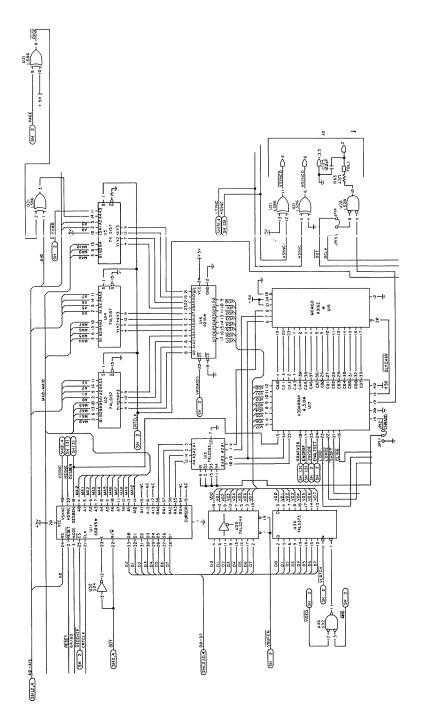

### 2.1.9 Keyboard

The interface to the keyboard is a matrix composed of address lines in one direction and data lines in the other. The address lines have two open collector buffers (U26 and U40) on the output to the keyboard.

The input is pulled-up with an 820 ohm resistor and is then fed into two CMOS Inputs (U55 and U56) which act as a driver on data lines.

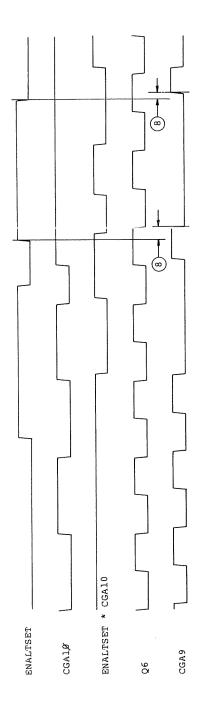

### 2.1.10 Real Time Clock

The Real Time Clock circuit in the Model 4 provides a 30 Hz (in the 2 MHz CPU Mode) or 60 Hz (in the 4 MHz CPU Mode) interrupt to the CPU By counting the number of interrupts that have occured, the CPU can keep track of the time. The 60 Hz vertical sync signal from the video circuitry is divided by two (2 MHz Mode) by U10 and the 30 Hz at pin 9 of U46 is used to generate the interrupts. In the 4 MHz mode, the signal FAST places a logic low at pin 4 of U10, causing the signal VSYNC to pass through U46 at its normal rate and trigger interrupts at the 60 Hz rate. Note that any time interrupts are disabled, the accuracy of the clock suffers.

### 2.1.11 Line Printer Port

The printer status lines are read by the CPU by enabling buffer U108. This buffer will be enabled for any input from port F8 or F9, or any memory read from location 37E8 or 37E9 when in the Model III mode. For a listing of bit status, refer to the bit map

After the printer driver software determines that the printer is ready to receive a character (by reading the status), the character to be printed is output to port F8 This latches the character into U107, and simultaneously fires the one-shot U63 to provide the appropriate strobe to the printer.

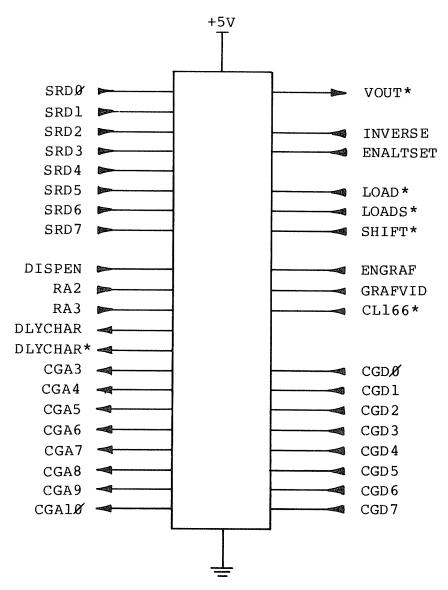

### 2.1.12 Graphics Port

The graphics port on the Model 4 is provided to attach the optional high resolution graphics board and provides the necessary signals to interface not only to the CPU (such as data lines, address lines, address decodes, and control lines), but also the signals needed to synchronize the output of the Video Circuit and the Graphics board and control to provide features such as overlay.

| Pin Number | Signature |  |

|------------|-----------|--|

| 1          | D0        |  |

| 2          | D1        |  |

| 3          | D2        |  |

| 4          | D3        |  |

| 5          | D4        |  |

| 6          | D5        |  |

| 7          | D6        |  |

| 8          | D7        |  |

| 9          | GEN*      |  |

| 10         | DCLK      |  |

| 11         | A0        |  |

| 12         | A1        |  |

| 13         | A2        |  |

| 14         | J         |  |

| 15         | GRAPVID   |  |

| 16         | ENGRAF    |  |

| 17         | DISBEN    |  |

| 18         | VSYNC     |  |

| 19         | HSYNC     |  |

| 20         | RESET*    |  |

| 21         | WAIT*     |  |

| 22         | Н         |  |

| 23         | I         |  |

| 24         | IN*       |  |

| 25         | GND       |  |

| 26         | +5        |  |

| 27         | N/C       |  |

| 28         | CL166     |  |

| 29         | GND       |  |

| 30         | +5        |  |

| 31         | GND       |  |

| 32         | +5        |  |

| 33         | GND       |  |

| 34         | +5        |  |

|            |           |  |

Table 2-5

Figure 2-17. Keyboard (Page 4 of Schematic)

Figure 2-18. RTC (Page 4 of Schematic)

Figure 2-19. Printer Circuit

### (Page 4 of Schematic)

Figure 2-20. Sound

(Page 4 of Schematic)

### 2.1.13 Sound Port

The sound circuit is compatible with the optional sound board on the older version of the Model 4, and works in a similar fashion. Sound is generated by setting and clearing data bit zero on successive OUTs to port 90H. The state of D0 is latched in U18 which is amplified by Q2 to drive the speaker (SP1).

### 2.1.14 I/O Bus Port

The Model 4 Gate Array Bus is designed to allow easy and convenient interfacing of I/O devices to the Model 4. The I/O Bus supports all the signals necessary to implement a device compatible with the Z-80s I/O structure. That is:

### Addresses:

A0 to A7 allow selection of up to 256 input and 256 output devices if external I/O is enabled

Ports 80H to 0FFH are reserved for System use

### Data:

DB0 to DB7 allow transfer of 8-bit data onto the processor data bus if external I/O is enabled

### Control Lines:

- a IN\* Z-80 signal specifying that an input is in progress. Gated with IORQ.

- b. OUT\* Z-80 signal specifying that an output is in progress. Gated with IORQ

- c RESET\* -- system reset signal.

- d. IOBUSINT\* input to the CPU signaling an interrupt from an I/O Bus device if I/O Bus interrupts are enabled.

- e IOBUSWAIT\* input to the CPU wait line allowing I/O Bus device to force wait states on the Z-80 if external I/O is enabled

- f EXTIOSEL\* input to CPU which switches the I/O Bus data bus transceiver and allows an INPUT instruction to read I/O Bus data

- g. M1\* and IORQ\* standard Z-80 signals.

The address line, data line, and control lines a to c and e to g are enabled only when the ENEXIO bit is set to a one.

To enable I/O interrupts, the ENIOBUSINT bit in the CPU IO-PORT E0 (output port) must be a one. However, even if it is disabled from generating interrupts, the status of the IOBU-SINT\* line can still read on the appropriate bit of CPU IO-PORT E0 (input port)

See Model 4 Port Bit assignment for 0FF, 0EC, and 0E0.

The Model 4 CPU board is fully protected from foreign I/O devices in that all the I/O bus signals are buffered and can be disabled under software control. To attach and use an I/O device on the I/O Bus, certain requirements (both hardware and software) must be met

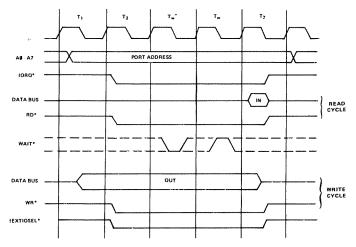

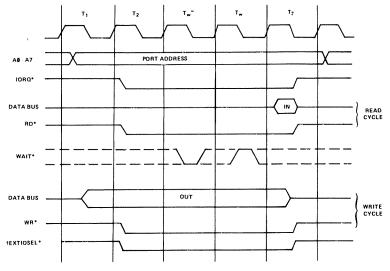

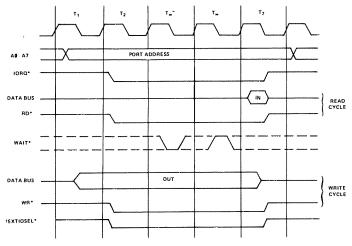

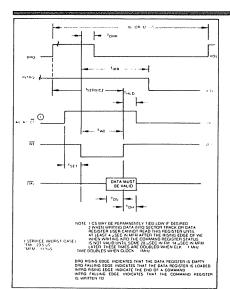

For input port device use, you must enable external I/O devices by writing to port OECH with bit 4 on in the user software This will enable the data bus, address lines, and control signals to the I/O Bus edge connector. When the input device is selected, the hardware will acknowledge by asserting EXTIOSEL\* low This switches the data bus transceiver and allows the CPU to read the contents of the I/O Bus data lines See Figure 2-21 for the timing EXTIOSEL\* can be generated by MANDing IN and the I/O port address

Output port device use is the same as the input port device in use, in that the external I/O devices must be enabled by writing to port OECH with bit 4 on in the user software — in the same fashion

For either input or output devices, the IOBUSWAIT\* control line can be used in the normal way for synchronizing slow devices to the CPU Note that since dynamic memories are used in the Model 4, the wait line should be used with caution Holding the CPU in a wait state for 2 msec or more may cause loss of memory contents since refresh is inhibited during this time. It is recommended that the IOBUSWAIT\* line be held active no more than 500 msec with a 25% duty cycle

The Model 4 will support Z-80 mode 1 interrupts A RAM jump table is supported by the LEVEL II BASIC ROMs and the user must supply the address of his interrupt service routine by writing this address to locations 403E and 403F. When an interrupt occurs, the program will be vectored to the user supplied address if I/O Bus interrupts have been enabled. To enable I/O Bus interrupts, the user must set bit 3 of Port 0EOH.

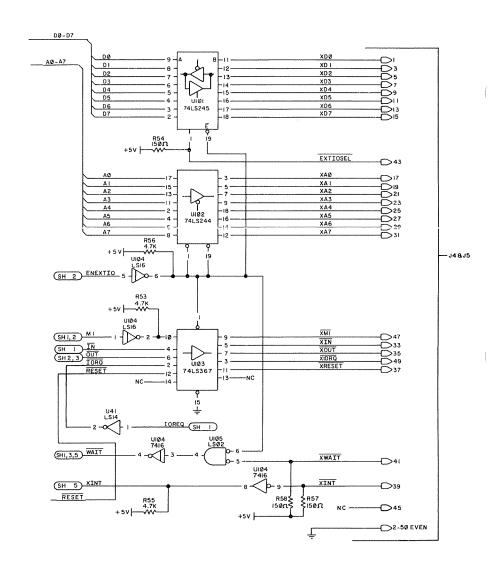

The actual implementation is shown in Figure 2-22 The data is buffered in both directions using a 74LS245 (U101). The addresses are buffered with a 74LS244 (U102), and the control lines out are buffered by a 74LS367. Note that RE-SET\* is always enabled out, this is to power-up reset any device or clear any device before enabling the bus structure. This prevents any user from tying-up the bus when enabling the port in an unknown state.

"Inserted by Z80 CPU

Input or Output Cycles with Wait States.

"Inserted by Z80 CPU

†Coincident with IORQ® only on INPUT cycle

Figure 2-21. I/O BUS TIMING DIAGRAM

Figure 2-22. I/O Port (Page 4 of Schematic)

| Data Bit | Function                                                           |

|----------|--------------------------------------------------------------------|

| D0       | Selects Drive 0 when set*                                          |

| D1       | Selects Drive 1 when set*                                          |

| D2       | Selects Drive 2 when set*                                          |

| D3       | Selects Drive 3 when set*                                          |

| D4       | Selects Side 0 when reset                                          |

|          | Selects Side 1 when set                                            |

| D5       | Write precompensation<br>enabled when set dis-<br>abled when reset |

| D6       | Generates WAIT if set                                              |

| D7       | Selects MFM mode if set                                            |

|          | Selects FM mode if reset                                           |

<sup>\*</sup>Only one of these bits should be set per output

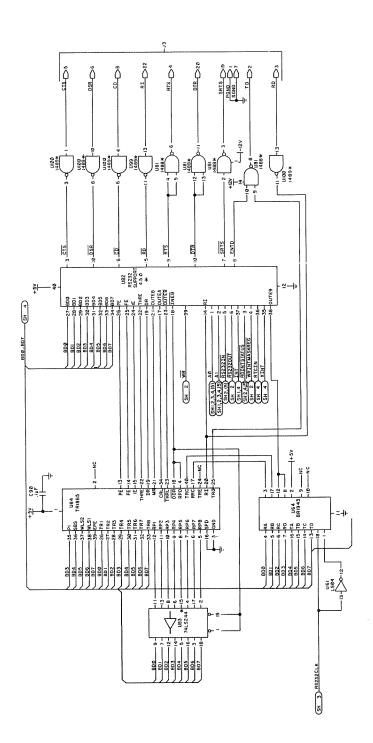

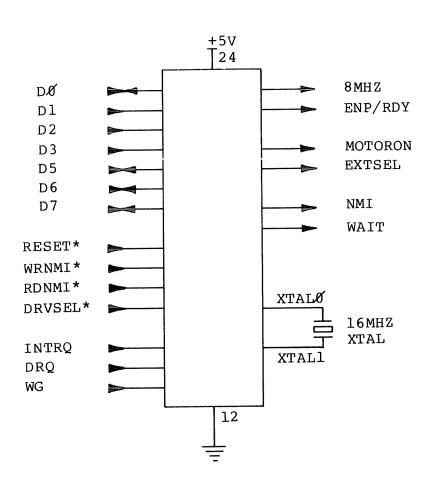

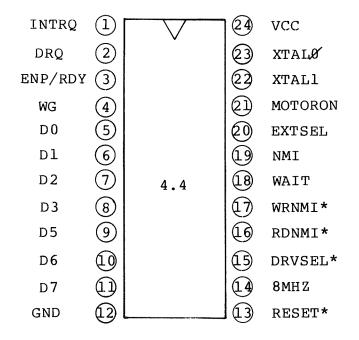

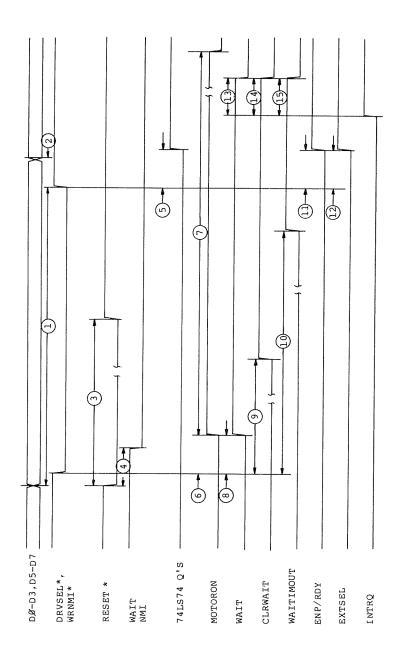

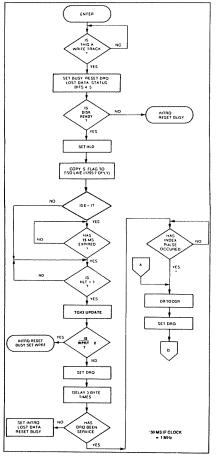

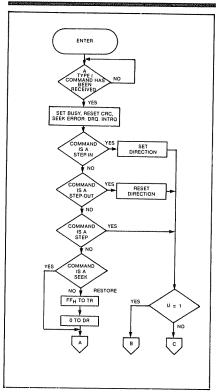

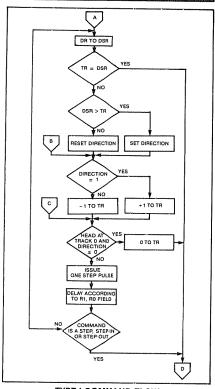

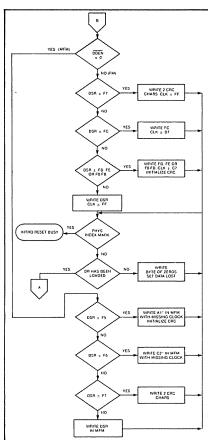

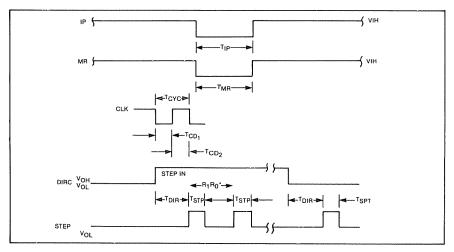

Hex D flip-flop U79 (74L174) latches the drive select bits, side select and FM\* MFM bits on the rising edge of the control signal DRVSEL\* Gate Array 4.4(U76) is used to latch the Wait Enable and Write precompensation enable bits on the rising edge of DRVSEL\*. The rising edge of DRVSEL\* also triggers a one-shot (Internal to U76) which produces a Motor On to the disk drives The duration of the Motor On signal is approximately three seconds The spindle motors are not designed for continuous operation. Therefore, the inactive state of the Motor On signal is used to clear the Drive Select Latch, which de-selects any drives which were previously selected. The Motor On one-shot is retriggerable by simply executing another OUT instruction to the Drive Select Latch.

### Wait State Generation and WAITIMOUT Logic

As previously mentioned, a wait state to the CPU can be initiated by an OUT to the Drive Select Latch with D6 set Pin 10 of U76 will go high after this operation. This signal is inverted by 1/4 of U96 and is routed to the CPU where it forces the Z80A into a wait state. The Z80A will remain in the wait state as long as WAIT\* is low. Once initiated, the WAIT\* will remain low until one of five conditions is satisfied. If INTRQ, DRQ, or RESET inputs become active (logic high), it causes WAIT\* to go high which allows the Z80 to exit the wait state. An internal timer on U70 serves as a watchdog timer to insure that a wait condition will not persist long enough to destroy dynamic RAM contents. This internal watchdog timer logic will limit the duration of a wait to 1024 μsec, even if the FDC chip should fail to generate a DRQ or an INTRQ.

If an OUT to Drive Select Latch is initiated with D6 reset (logic low), a WAIT is still generated. The internal timer on U70 will count to 2 which will clear the WAIT state. This allows the WAIT to occur only during the OUT instruction to prevent violating any Dynamic RAM parameters.

NOTE: This automatic WAIT will cause a 5 to 1 µsec wait each time an out to Drive Select Latch is performed.

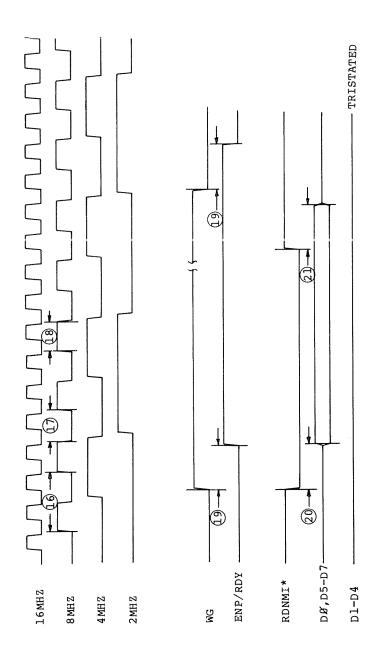

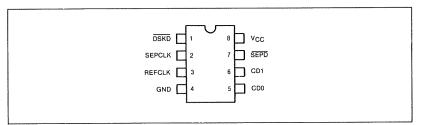

### **Clock Generation Logic**

A 16 MHz crystal oscillator and Gate Array 4.4 (U76) are used to generate the clock signals required by the FDC board. The 16 MHz oscillator is implemented internal to U76 and a quartz crystal (Y2). The output of the oscillator is divided by 2 to generate on 8 MHz clock. This is used by the FDC 1773 (U75) for all internal timing and data separation U76 further divides the 16 MHz clock to drive the watchdog timer circuit.

### Disk Bus Output Drivers

High current open collector drivers U96, 94 and 93 are used to buffer the output signals from the FDC circuit to the disk drives

## Write Precompensation and Write Data Pulse Shaping Logic

All write precompensation is generated internal to the FDC chip 1773 (U75). Write Precompensation occurs when WG goes high and write precompensation is enabled from the software. ENP is multiplexed with RDY and is controlled by WG at pin 20 of U75 Write data is output on pin 22 of U75 and is shaped by a one-shot (1/2 of U98) which stretches the data pulses to approximately 500 nsec

### Clock and Read Data Recovery Logic

The Clock and Read Data Recovery Logic is done internal to the 1773 (U75).

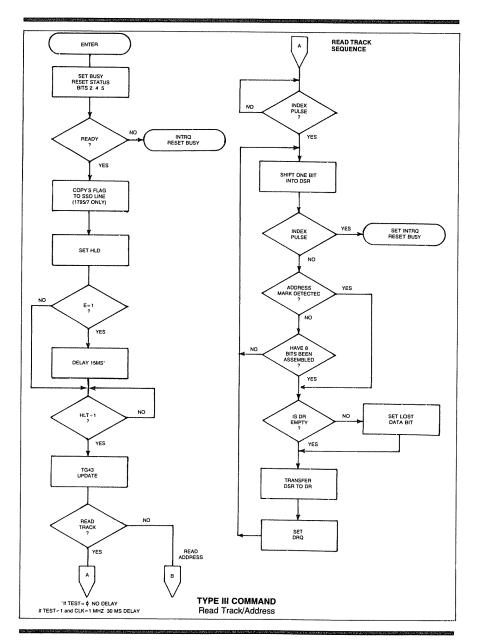

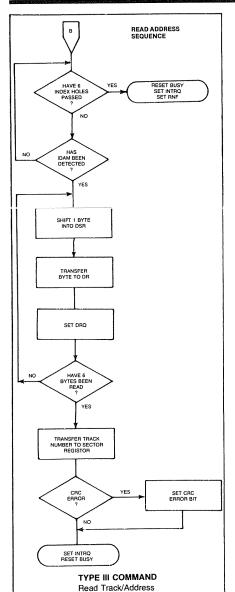

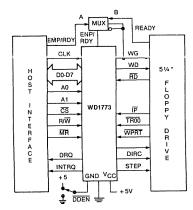

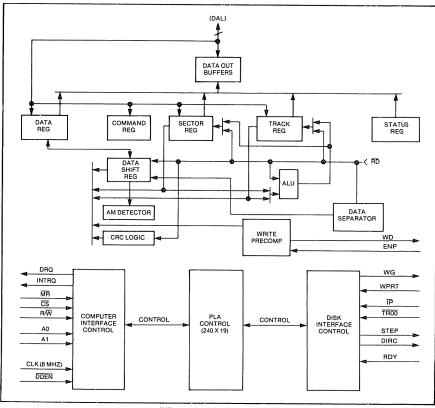

### Floppy Disk Controller Chip

The 1773 is an MOS LSI device which performs the functions of a floppy disk formatter/controller in a single chip implementation. The following port addresses are assigned to the internal registers of the 1773 FDC chip:

| Port No. | Function                   |

|----------|----------------------------|

| F0H      | Command/Status<br>Register |

| F1H      | Track Register             |

| F2H      | Sector Register            |

| F3H      | Data Register              |

|          |                            |

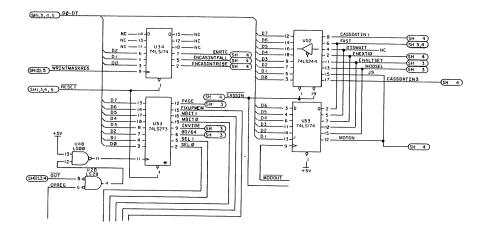

### 2.1.15 Cassette Circuit

The cassette write circuitry latches the two LSBs (D0 and D1) for any output to port FF (hex). The outputs of these latches (U51) are then resistor summed to provide three discrete voltage levels (500 Baud only). The firmware toggles the bits to provide an output signal of the desired frequency at the summing node.

There are two types of cassette Read circuits — 500 baud and 1500 baud. The 500 baud circuit is compatible with both Model I and III. The input signal is amplified and filtered by Op amps (U23 and U54). Part of U22 then forms a Zero Crossing Detector, the output of which sets the latch U37. A read of Port FF enables buffer U52 which allows the CPU to determine whether the latch has been set, and simultaneously resets the latch. The firmware determines by the timing between settings of the latch whether a logic "one" or "zero" was read in from the tape.

The 1500 baud cassette read circuit is compatible with the Model III cassette system. The incoming signal is compared to a threshold by part of U22 U22's output will then be either high or low and clock about one-half of U37, depending on whether it is a rising edge or a falling edge If interrupts are enabled, the setting of either latch will generate an interrupt. As in the 500 baud circuit, the firmware decodes the interrupts into the appropriate data

For any cassette read or write operation, the cassette relay must be closed in order to start the motor of the cassette deck. A write to port EC hex with bit one set will latch U53, which turns on transistor Q3 and energizes the relay K1. A subsequent write to this port with bit one clear will clear the latch and de-energize the relay.

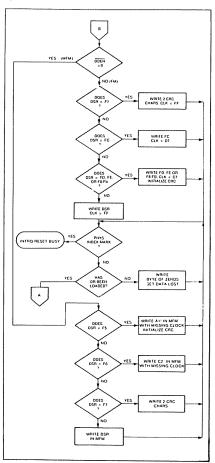

### 2.1.16 FDC Circuit

The TRS-80 Model 4 Floppy Disk Interface provides a standard 5-1/4" floppy disk controller. The Floppy Disk Interface supports single and double density encoding schemes. Write precompensation can be software enabled or disabled beginning at any track, although the system software enables write precompensation for all tracks greater than twenty-one The amount of write precompensation is 125 nsec and is not adjustable. One to four drives may be controlled by the interface. All data transfers are accomplished by CPU data requests. In double density operation, data transfers are synchronized to the CPU by forcing a wait to the CPU and clearing the wait by a data request from the FDC chip. The end of the data transfer is indicated by generation of a nonmaskable interrupt from the interrupt request output of the FDC chip. A hardware watchdog timer insures that any error condition will not hang the wait line to the CPU for a period long enough to destroy RAM contents.

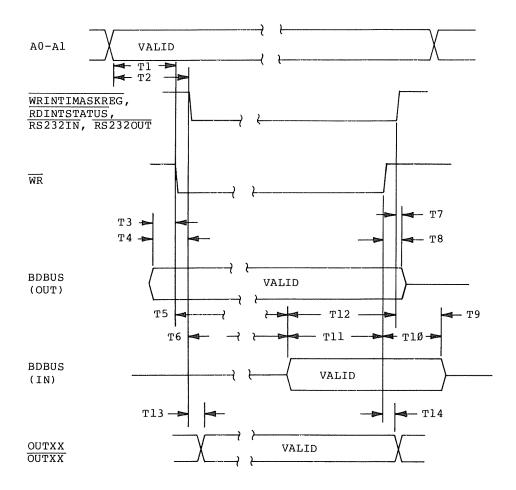

### **Control and Data Buffering**

The Floppy Controller is an I/O port-mapped device which utilizes ports E4H, F0H, F1H, F2H, F3H, and F4H. The decoding logic is implemented in the Address Decoding (for more information see Port Map) U78 is a bi-directional, 8-bit transceiver used to buffer data to and from the FDC and RS-232 circuits The direction of data transfer is controlled by the combination of control signals DISKIN\*, RDINTSTA-TUS\*, RDNINSTATUS\*, and RS232IN\* If any signal is active (logic low), U78 is enabled to drive data onto the CPU data bus If all signals are inactive (logic high), U78 is enabled to receive data from the CPU board data bus. A second buffer U77 is used to buffer the FDC chip data to the FDC/RS232 Data Bus, (BD0-BD7). U77 is enabled by Chip Select and its direction controlled by DISKIN\* Again, if DISKIN\* is active (logic low), data is enabled to drive from the FDC chip to the Main Data Busses. If DISKIN\* is inactive (logic high), data is enabled to be transferred to the FDC chip.

### Non-maskable Interrupt Logic

Gate Array 4.4 (U75) is used to latch data bits D6 and D7 on the rising edge of the control signal WRNMIMASKREG\* This enables the conditions which will generate a non-maskable interrupt to the CPU. The NMI interrupt conditions which are programmed by doing an OUT instruction to port E4H with the appropriate bits set. If data bit 7 is set, an FDC interrupt is enabled to generate an NMI interrupt. If data bit 7 is reset, interrupt requests from the FDC are disabled. If data bit 6 is set, a Motor Time Out is enabled to generate an NMI interrupt. If data bit 6 is reset, interrupts on Motor Time Out are disabled. An IN instruction from port E4H enables the CPU to determine the course of the non-maskable interrupt. Data bit 7 indicates the status of FDC interrupt request (INTRQ) (0 = true, 1 = false) Data bit 6 indicates the status of Motor Time Out (0 = true, 1 = false). Data bit 5 indicates the status of the Reset signal (0 = true, 1 = false). The control signal RDNMISTATUS\* gates this status onto the CPU data bus when active (logic low).

### **Drive Select Latch and Motor ON Logic**

Selecting a drive prior to disk I/O operation is accomplished by doing an OUT instruction to port F4H with the proper bit set. The following table describes the bit allocation of the Drive Select Latch:

Hardware 49

Figure 2-24. F.D.C. Circuit (Page 5 of Schematic)

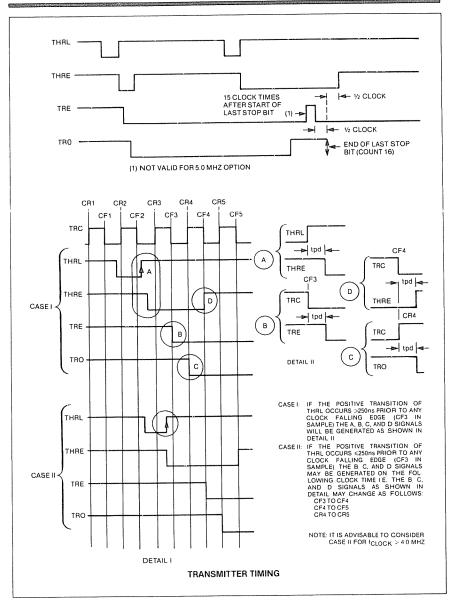

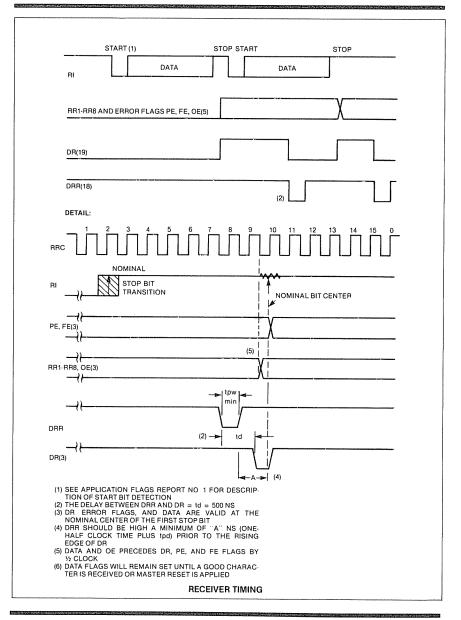

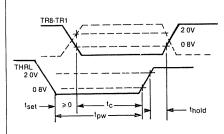

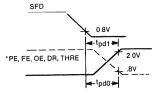

### **RS-232C Technical Description**

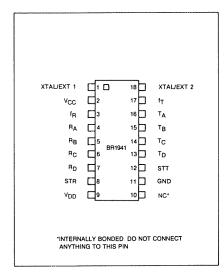

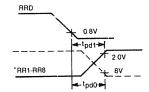

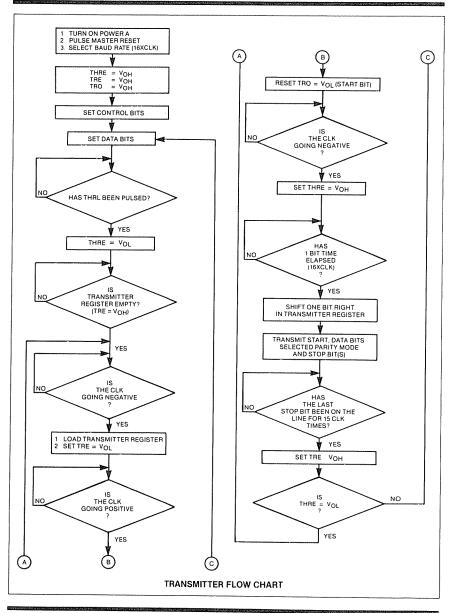

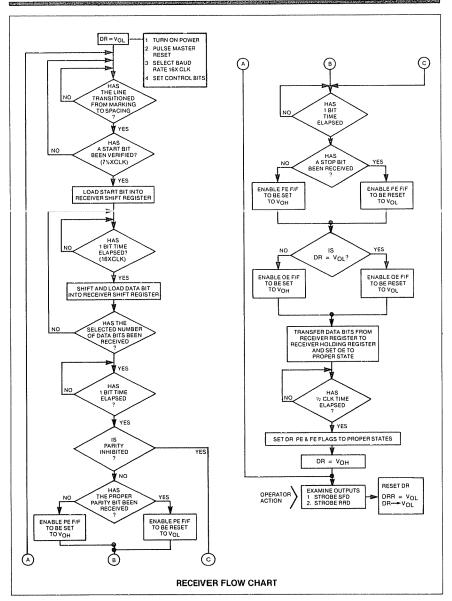

The RS-232C circuit for the Model 4 computer supports asynchronous serial transmissions and conforms to the EIA RS-232C standards at the input-output interface connector (J3). The heart of the circuit is the TR1865 Asynchronous Receiver/Transmitter U84. It performs the job of converting the parallel byte data from the CPU to a serial data stream including start, stop, and parity bits. For a more detailed description of how this LSI circuit performs these functions, refer to the TR1865 data sheets and application notes. The transmit and receive clock rates that the TR1865 needs are supplied by the Baud Rate Generator U104 This circuit takes the 5.0688 MHz supplied by the system timing circuit and the programmed information received from the CPU over the data bus and divides the basic clock rate to provide two clocks. The rates available from the BRG go from 50 Baud to 19200 Baud See the BRG table for the complete Interrupts are supported in the RS-232C Circuit by the Interrupt mask register and the Status register internal to Gate Array 4.5 (U82) The CPU looks here to see which kind of interrupt has occurred Interrupts can be generated on receiver data register full, transmitter register empty, and any one of the errors — parity, framing, or data overrun. This allows a minimum of CPU overhead in transferring data to or from the UART. The interrupt mask register is port EO (write) and the interrupt status register is port EO (read). Refer to the IO Port description for a full breakdown of all interrupts and their bit positions.

All Model I, III, and 4 software written for the RS-232C interface is compatible with the Model 4 Gate Array RS-232C circuit, provided the software does not use the sense switches to configure the interface The programmer can get around this problem by directly programming the BRG and UART for the desired configuration or by using the SETCOM command of the disk operating system to configure the interface The TRS-80 RS-232C Interface hardware manual has a good discussion of the RS-232C standard and specific programming examples (Catalog Number 26-1145)

### **BRG Programming Table**

| AULEL            | Transmit/<br>Receive | 16X        | Suported |

|------------------|----------------------|------------|----------|

| Nibble<br>Loaded | Baud<br>Rate         | Clock      | SETCOM   |

|                  |                      |            |          |

| oН               | 50                   | 0.8 kHz    | Yes      |

| 1H               | 75                   | 1.2 kHz    | Yes      |

| 2H               | 110                  | 1.76 kHz   | Yes      |

| 3H               | 134.5                | 2 1523 kHz | Yes      |

| 4H               | 150                  | 2.4 kHz    | Yes      |

| 5H               | 300                  | 4.8 kHz    | Yes      |

| 6H               | 600                  | 9.6 kHz    | Yes      |

| 7H               | 1200                 | 19.2 kHz   | Yes      |

| 8H               | 1800                 | 28.8 kHz   | Yes      |

| 9H               | 2000                 | 32.081 kHz | Yes      |

| AH               | 2400                 | 38.4 kHz   | Yes      |

| BH               | 3600                 | 57.6 kHz   | Yes      |

| CH               | 4800                 | 76.8 kHz   | Yes      |

| DH               | 7200                 | 115.2 kHz  | Yes      |

| EH               | 9600                 | 153.6 kHz  | Yes      |

| FH               | 19200                | 307.2 kHz  | Yes      |

### Pinout Listing

The RS-232C circuit is port mapped and the ports used are E8 to E8. Following is a description of each port on both input and output

The following list is a pinout description of the DB-25 connector (P1).

Pin No.

Signal

|      |                  |                         | 1  | PGND (Protective Ground)     |

|------|------------------|-------------------------|----|------------------------------|

| Port | Input            | Output                  | 2  | TD (Transmit Data)           |

| E8   | Modem status     | Master Reset, enables   | 3  | RD (Receive Data)            |

|      |                  | UART control register   | 4  | RTS (Request to Send)        |

|      |                  | load                    | 5  | CTS (Clear To Send)          |

| EA   | UART status      | UART control register   | 6  | DSR (Data Set Ready)         |

|      |                  | load and modem control  | 7  | SGND (Signal Ground)         |

| E9   | Not Used         | Baud rate register load | 8  | CD (Carrier Detect)          |

|      |                  | enable bit              | 19 | SRTS (Spare Request to Send) |

| EB   | Receiver Holding | Transmitter Holding     | 20 | DTR (Data Terminal Ready)    |

|      | register         | register                | 22 | BI (Ring Indicate)           |

Figure 2-25. RS232C Circuit (Page 5 of Schematic)

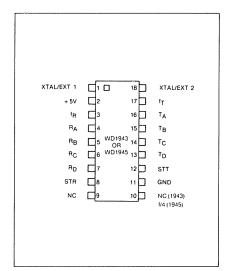

# Model 4 Gate Array I/O Pin Assignments